Главный недостаток комбинационная схема есть, он не использует память для сохранения текущего и предыдущего состояний. Следовательно, предыдущее состояние входа не влияет на текущее состояние схемы. Принимая во внимание, что последовательная схема имеет память, поэтому вывод может варьироваться в зависимости от ввода. Этот тип схем использует предыдущий ввод, вывод, часы и элемент памяти. Здесь элементы памяти могут быть защелками или триггерами. Последовательные схемы разрабатываются различными методами, например, с использованием ПЗУ и флипов, PLA, CPLD (сложное программируемое логическое устройство) , ПЛИС (программируемая вентильная матрица) . В этой статье мы собираемся обсудить только то, как создать последовательную схему с использованием PLA.

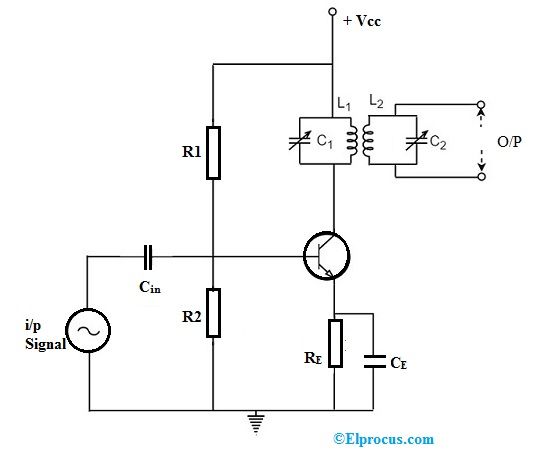

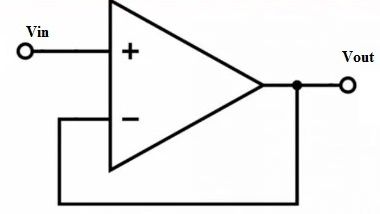

Блок-схема последовательной схемы показана ниже:

Блок-схема последовательной цепи

Проектирование последовательной схемы с использованием PLA

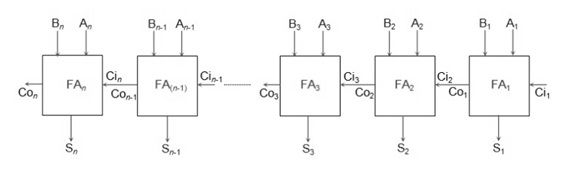

Последовательные схемы могут быть реализованы с использованием PLA (программируемых логических массивов) и триггеров. В этой схеме назначение состояния может быть важным, поскольку использование назначения хорошего состояния может уменьшить необходимое количество терминов продукта и, следовательно, уменьшить требуемый размер PLA. Термин продукта, определяемый как соединение литералов, где каждый литерал является либо переменной, либо ее отрицанием.

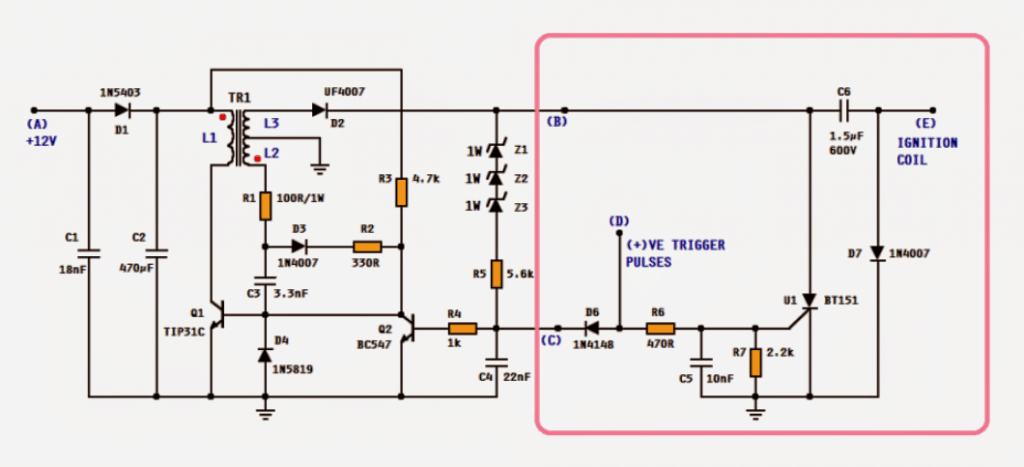

Ибо давайте рассмотрим дизайн конвертера кода. Таблица состояний, показанная ниже в таблице, может быть реализована с использованием одного PLA и трех шлепки как показано на рисунке ниже. Эта конфигурация схемы очень похожа на схему на основе триггера ПЗУ, за исключением того, что ПЗУ заменяется PLA подходящего размера. Назначение состояний приводит к таблице истинности, приведенной ниже. Эта таблица может быть сохранена в PLA с четырьмя входами, 13 терминами продукта и четырьмя выходами, но это немного уменьшит размер по сравнению с ПЗУ на 16 слов.

| X 1 квартал 2 квартал 3 квартал | С D1 D2 D3 |

| 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 | 1 0 0 1 1 0 1 1 0 1 0 0 0 1 0 1 1 1 0 1 0 0 0 0 1 0 0 0 Х Х Х Х 0 0 1 0 0 1 0 0 1 1 0 0 1 1 0 1 0 1 1 0 1 0 0 0 Х Х Х Х Х Х Х Х |

Таблица: Таблица истинности

НАСТОЯЩЕЕ ВРЕМЯ ГОСУДАРСТВЕННЫЙ

| СЛЕДУЮЩЕЕ СОСТОЯНИЕ Х = 0 1 | НАСТОЯЩЕЕ ВРЕМЯ ВЫХОД (Z) |

| К | ДО Н.Э | 1 0 |

B C | D E И E | 1 0 0 1 |

D ЯВЛЯЕТСЯ | H H H M | 0 1 1 0 |

ЧАС M | А А К - | 0 1 1 - |

Таблица: Таблица состояний

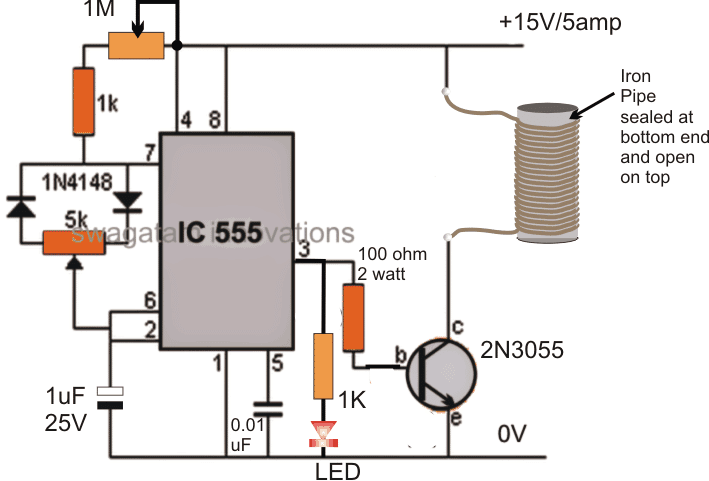

Проектирование последовательных цепей с использованием PLA

Входные выходные уравнения, полученные с помощью карты Карно

Здесь, поскольку имеется семь состояний, требуются три D-триггера. Таким образом, требуется схема PLA с 4 входами и 4 выходами. Если рассматривать присвоение состояний преобразователя кода, то результирующее выходное уравнение и входные уравнения D-триггера, полученные из Карно, можно записать в следующие уравнения:

D1 = Q1 + = Q2 »

D2 = Q2 + = Q2 »

D3 = Q3 + = Q1 Q2 Q3 = X 'Q1 Q3' = X Q1 'Q2'

Z = X 'Q3' + X Q3

| X 1 квартал 2 квартал 3 квартал | С D1 D2 D3 |

- - 0 - - 1 - - - 1 1 1 0 1 - 0 1 0 0 - 0 - - 0 11

| 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 1 0 0 0

|

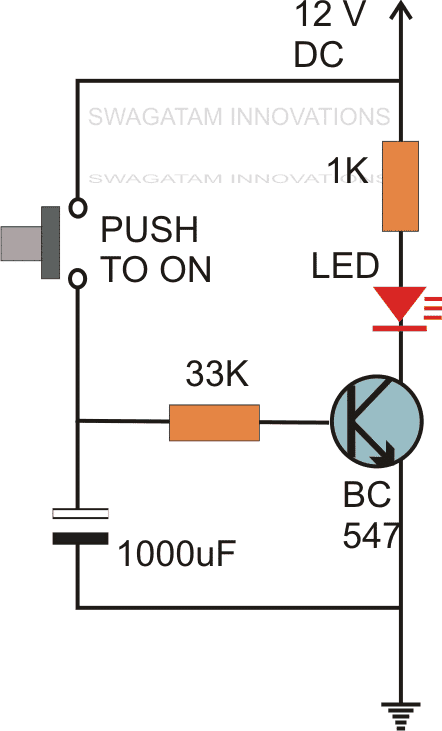

Таблица PLA, соответствующая этим уравнениям, приведена в таблице выше. Эта таблица может быть реализована с помощью PLA с четырьмя входами, семью терминами продукта и четырьмя выходами. Чтобы сначала проверить работу вышеуказанной схемы, предположим, что X = 0 и Q1Q2Q3 = 000. Это выбирает строки - - 0- и 0 - - -0 в таблице, поэтому Z = 0 и D1D2D3 = 100. После активного фронта тактового сигнала Q1Q2Q3 = 100. Если следующий вход - X = 1, то выбираются строки - - 0 - и - 1-, поэтому Z = 0 и D1D2D3 = 110. После активного фронта тактового сигнала Q1Q2Q3 = 110.

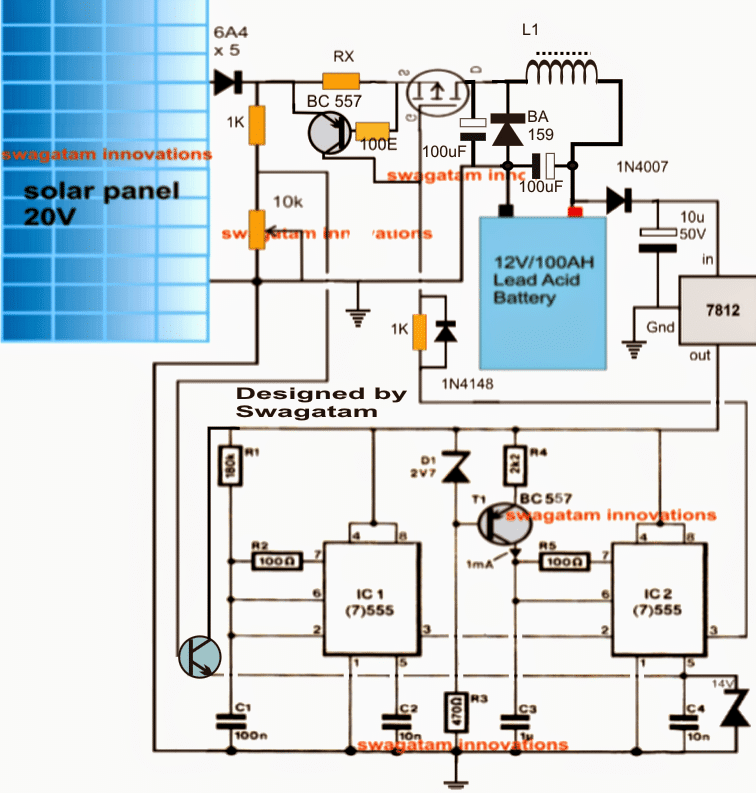

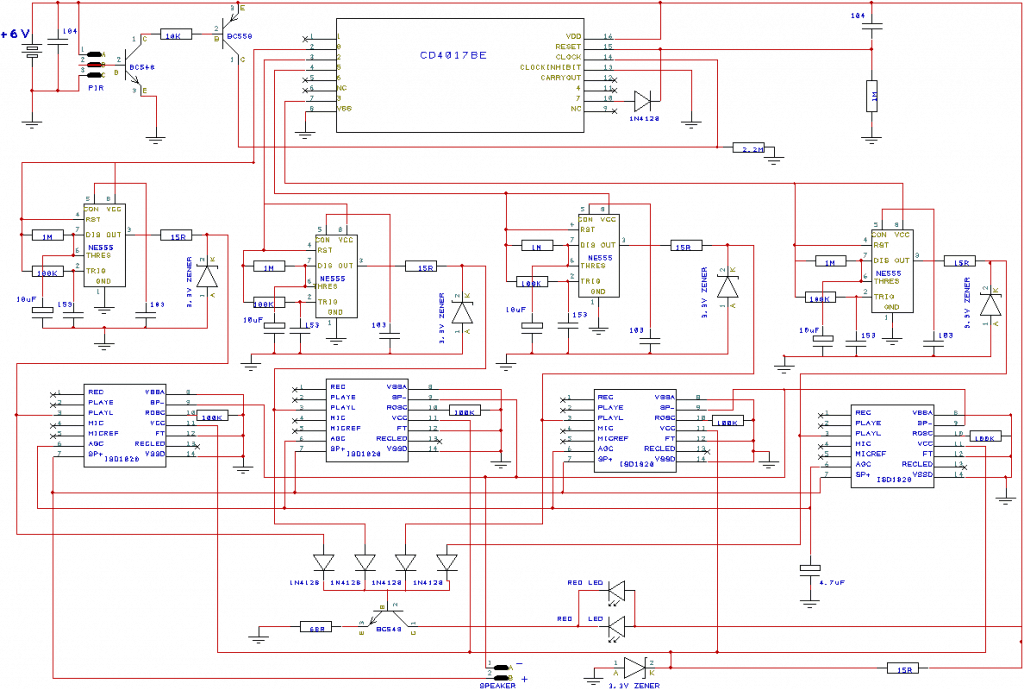

Программируемый логический массив (PLA)

Programmable Logic Array - это программируемое логическое устройство. Обычно он используется для реализации схем комбинационной логики. PLA имеет набор программируемых плоскостей И (массив И), которые связаны с набором программируемых плоскостей ИЛИ (массив ИЛИ), которые затем могут быть временно дополнены для получения выходных данных. Такая компоновка позволяет синтезировать большое количество логических функций в сумма продуктов (СОП) канонические формы. Ниже приведена простая блок-схема PLA.

Блок-схема PLA

Основное различие между PLA и PAL (логика программируемого массива) заключается в следующем:

PLA: Оба И самолет и ИЛИ самолет программируются.

PAL: Программируется только плоскость И, а плоскость ИЛИ - фиксированная.

Для лучшего понимания PLA рассмотрим приведенный ниже пример.

Давайте попробуем реализовать эти функции. F1 и f2 задаются как

Входы x1, x2, x3 и соответствующие им дополненные сигналы передаются в программируемую плоскость И, там мы получим выходы плоскости И как P1, P2, P3, называемые minterms. Затем эти сигналы подаются на программируемую плоскость ИЛИ для получения требуемой выходной функции f1 и f2 (сумма произведений). На приведенном ниже рисунке описана реализация PLA на уровне шлюза для заданной функциональности.

Реализация PLA

Это все о проектировании последовательных цепей с использованием PLA. Мы считаем, что информация, представленная в этой статье, поможет вам лучше понять эту концепцию. Кроме того, любые вопросы по этой статье или помощь в реализация проектов в области электротехники и электроники , вы можете связаться с нами, оставив комментарий в разделе комментариев ниже. Вот вам вопрос, Что подразумевается под последовательной схемой?