За последние несколько лет процесс проектирования цифрового оборудования сильно изменился. Таким образом, небольшие цифровые схемы могут быть реализованы с использованием PAL и PLA. Каждое устройство используется реализовать различные схемы для которых не требуется больше, чем количество входов / выходов, выходов / выходов и условий продукта, которые предлагаются в конкретном чипе. Эти микросхемы не соответствуют довольно скромным размерам, обычно они поддерживают общее количество входов и выходов не более 32. Для проектирования этих схем, требующих большего количества входов и выходов, можно использовать либо многочисленные PLA / PAL, либо более стильный тип. Микросхемы можно использовать под названием CPLD (сложное программируемое логическое устройство). Микросхема CPLD включает в себя несколько схемных блоков на одной микросхеме с ресурсами внутренней проводки для присоединения схемных блоков. Каждый блок схемы сопоставим с PLA или PAL.

Что такое сложное программируемое логическое устройство?

Аббревиатура CPLD - «Сложные программируемые логические устройства», это один вид интегральной схемы что разработчики приложений разрабатывают для реализации цифрового оборудования, например мобильных телефонов. Они могут обрабатывать заведомо более высокие конструкции, чем SPLD (устройства с простой программируемой логикой), но предлагают меньше логики, чем FPGA ( программируемые вентильные матрицы CPLD включают в себя многочисленные логические блоки, каждый из которых включает 8-16 макроячеек. Поскольку каждый логический блок выполняет определенную функцию, все макроячейки в логическом блоке полностью связаны. В зависимости от использования эти блоки могут быть или не могут быть соединены друг с другом.

Комплексное программируемое логическое устройство

Большинство CPLD (сложных программируемых логических устройств) имеют макроячейки с суммой логической функции и выборочной FF (триггер) . В зависимости от микросхемы функция комбинаторной логики поддерживает от 4 до 16 элементов продукта с включением разветвления. CPLD также различаются регистрами сдвига и логическими вентилями. По этой причине вместо ПЛИС можно использовать CPLD с огромным количеством логических вентилей. Другая спецификация CPLD означает количество условий продукта, которые может выполнить макроячейка. Термины продукта являются продуктом цифровых сигналов, которые выполняют определенную логическую функцию.

CPLD доступны в нескольких формах пакетов IC и логических семействах. CPLD также различаются по напряжению питания, рабочему току, току в режиме ожидания и рассеиваемой мощности. Кроме того, их можно получить с различным объемом памяти и различными видами поддержки памяти. Обычно память выражается в битах / мегабитах. Поддержка памяти состоит из ПЗУ, ОЗУ и двухпортовой ОЗУ. Он также включает в себя CAM (память с адресацией по содержимому), а также память FIFO (первый пришел, первый ушел) и память LIFO (последний пришел, последний ушел).

Архитектура сложного программируемого логического устройства

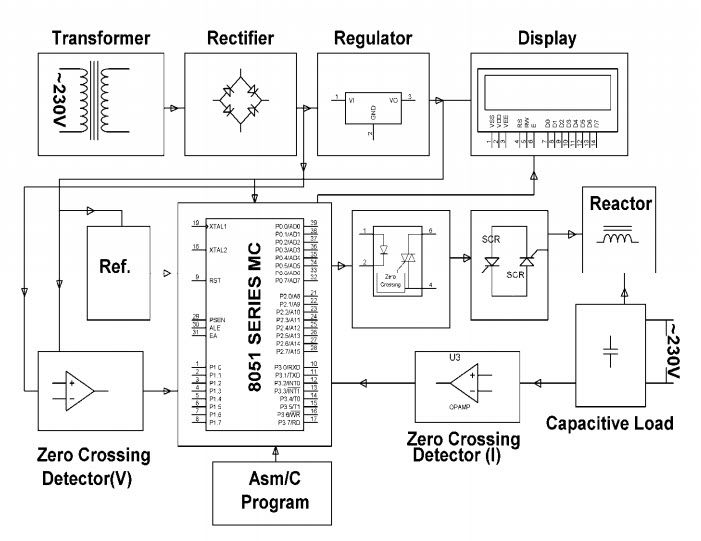

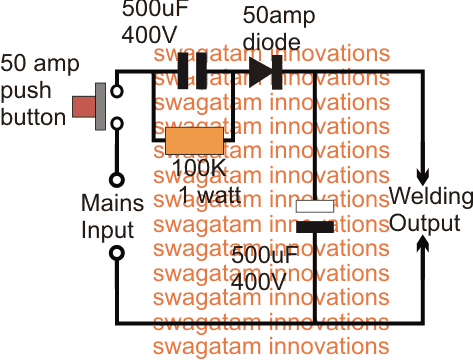

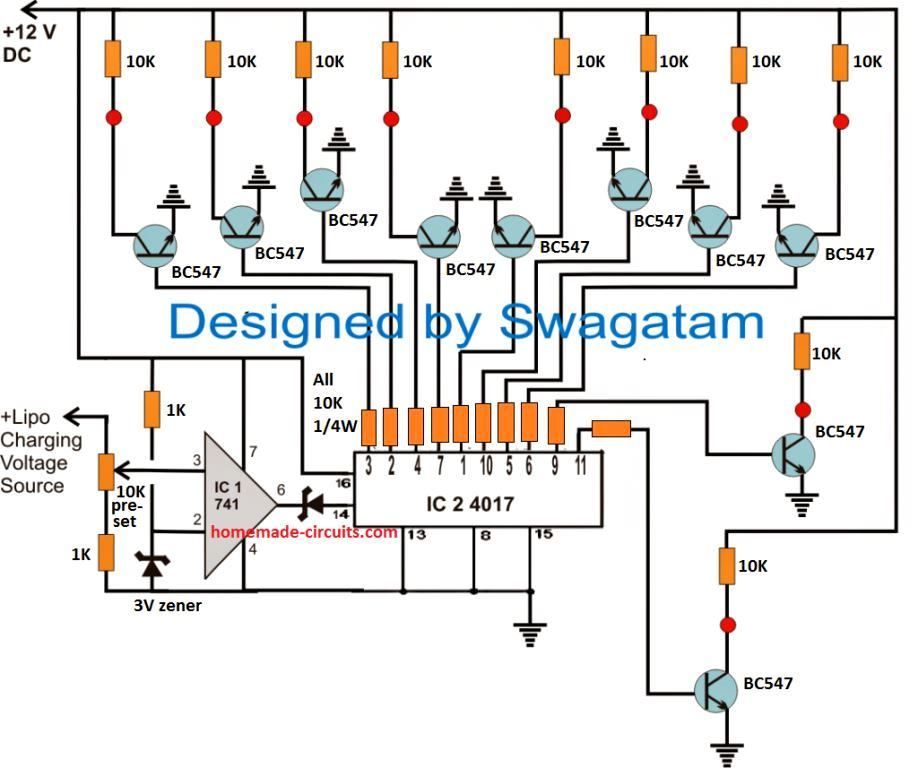

Сложное программируемое логическое устройство состоит из группы программируемых FB (функциональных блоков). Входы и выходы этих функциональных блоков связаны между собой посредством GIM (глобальной матрицы взаимосвязей). Эта матрица взаимосвязей реконфигурируема, так что мы можем изменять контакты между функциональными блоками. Будут некоторые блоки ввода и вывода, которые позволят нам объединить CPLD с внешним миром. Архитектура CPLD показана ниже.

В целом программируемый FB выглядит как массив логических вентилей , где можно запрограммировать массив элементов И, а элементы ИЛИ являются стабильными. Но у каждого производителя свой взгляд на дизайн функционального блока. Перечисленные o / p можно найти, управляя сигналами обратной связи, полученными с выходов логического элемента ИЛИ.

Архитектура CPLD

В программировании CPLD дизайн сначала кодируется на языке Verilog или VHDL после того, как код (моделируется и синтезируется. Во время синтеза вручную выбирается модель CPLD (целевое устройство) и создается список цепей сопоставления на основе технологии. Этот список можно закрыть -подгонка к подлинной архитектуре CPLD с использованием процесса размещения и маршрута, обычно реализуемого программным обеспечением размещения и маршрута собственной разработки компании CPLD. Затем оператор выполняет некоторые процессы подтверждения. Если все в порядке, он будет использовать CPLD, в противном случае он это переставит.

Проблемы архитектуры CPLD

При рассмотрении сложного программируемого логического устройства для использования в дизайне необходимо учитывать следующие архитектурные проблемы.

- Технология программирования

- Возможности функционального блока

- Возможности ввода / вывода

Некоторые из семейств CPLD от разных розничных продавцов включают

- Семейства Altera MAX 7000 и MAX 9000

- Семейства ATF и ATV Atmel

- Семейство решетчатых БИС isp

- Решетки (Vantis) семейства MACH

- Семейство Xilinx XC9500

Семейства CPLD

Приложения CPLD

Приложения CPLD включают следующие

- Сложные программируемые логические устройства идеально подходят для высокопроизводительных критически важных приложений управления.

- CPLD может использоваться в цифровых проектах для выполнения функций загрузчика

- CPLD используется для загрузки данных конфигурации программируемой вентильной матрицы из энергонезависимой памяти.

- Как правило, они используются в небольших дизайнерских приложениях, таких как декодирование адресов.

- CPLD часто используются во многих приложениях, например, в чувствительных к стоимости портативных устройствах с батарейным питанием из-за их небольшого размера и низкого потребления энергии.

Таким образом, речь идет о сложной архитектуре программируемого логического устройства и его приложениях. Мы надеемся, что вы лучше понимаете эту концепцию. Кроме того, любые вопросы относительно этой концепции или реализовать любые электротехнические и электронные проекты , пожалуйста, дайте свои ценные предложения, комментируя в разделе комментариев ниже. Вот вам вопрос, в чем разница между CPLD и FPGA?

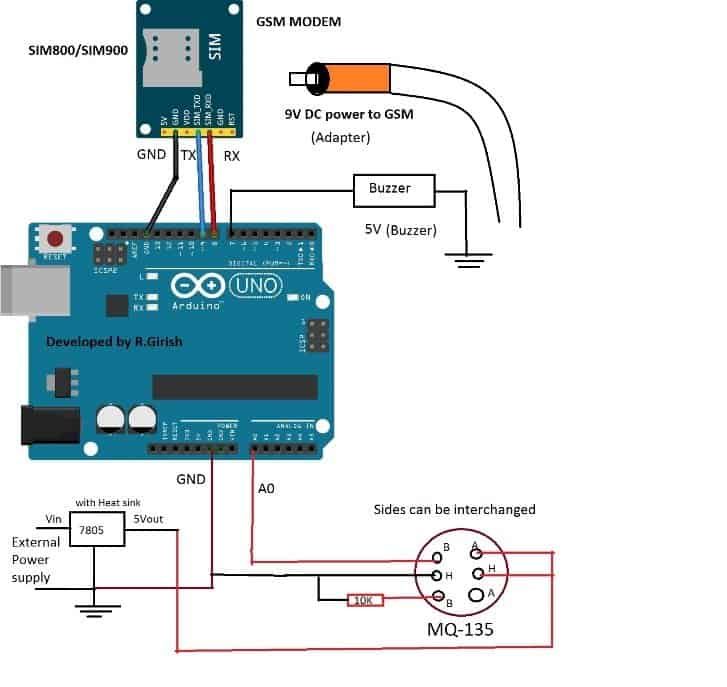

Фото: