Была эпоха, когда компьютеры были такими гигантскими по размеру, что для их установки требовалось место в комнате. Но сегодня они настолько развиты, что их можно легко носить даже как ноутбуки. Инновация, которая сделала это возможным, была концепция интегральных схем. В Интегральные схемы , большое количество активных и пассивные элементы вместе с их межсоединениями разрабатываются на небольшой кремниевой пластине, обычно размером 50 на 50 мил в поперечном сечении. Основные процессы, применяемые для изготовления таких схем, включают эпитаксиальный рост, диффузию замаскированных примесей, рост оксидов и травление оксидов с использованием фотолитографии для создания рисунка.

Компоненты на пластине включают резисторы, транзисторы, диоды, конденсаторы и т. Д. Самым сложным элементом в изготовлении микросхем являются транзисторы. Транзисторы бывают разных типов такие как CMOS, BJT, FET. Мы выбираем тип транзисторной технологии, которая будет реализована на ИС, исходя из требований. В этой статье познакомимся с концепцией Изготовление CMOS (или) изготовление транзисторов в виде КМОП.

Изготовление CMOS

Для меньшего рассеивания мощности CMOS технология используется для реализации транзисторов. Если нам нужна более быстрая схема, тогда транзисторы реализуются по IC с использованием BJT . Изготовление КМОП транзисторы как IC можно сделать тремя разными способами.

Технология N-лунки / P-лунки, где диффузия n-типа выполняется по подложке p-типа или диффузия p-типа выполняется по подложке n-типа соответственно.

В Технология Twin Well , куда NMOS и транзистор PMOS проявляются по пластине путем одновременной диффузии по эпитаксиальной ростовой основе, а не по подложке.

Процесс «Кремний на изоляторе», при котором вместо кремния в качестве подложки используется изолирующий материал для повышения скорости и восприимчивости к защелкиванию.

Технология N- well / P- well

КМОП можно получить, объединив оба NMOS и PMOS транзисторы над той же кремниевой пластиной. В технологии N-лунки лунка n-типа рассеивается на подложке p-типа, тогда как в P-лунке - наоборот.

Этапы изготовления CMOS

В CMOS процесс изготовления поток выполняется с использованием двадцати основных этапов изготовления при производстве с использованием технологии N-well / P-well.

Изготовление CMOS с использованием N well

Шаг 1: Сначала выбираем подложку в качестве основы для изготовления. Для N-лунки выбрана кремниевая подложка P-типа.

Субстрат

Шаг 2 - Окисление: Селективная диффузия примесей n-типа достигается с использованием SiO2 в качестве барьера, который защищает части пластины от загрязнения подложки. SiOдваразмещается в процессе окисления, при котором субстрат подвергается воздействию высококачественного кислорода и водорода в камере окисления при температуре примерно 10000c

Окисление

Шаг 3 - Выращивание фоторезиста: На этом этапе для селективного травления слой SiO2 подвергают процессу фотолитографии. В этом процессе пластина покрывается однородной пленкой светочувствительной эмульсии.

Выращивание фоторезиста

Шаг 4 - Маскировка: Этот шаг является продолжением процесса фотолитографии. На этом этапе с помощью трафарета делается желаемый узор открытости. Этот трафарет используется как маска поверх фоторезиста. Теперь субстрат подвергается воздействию УФ-лучи фоторезист, находящийся под открытыми участками маски, полимеризуется.

Маскировка фоторезиста

Шаг 5 - Удаление неоткрытого фоторезиста: Маска удаляется, а неэкспонированная область фоторезиста растворяется, проявляя пластину с использованием химического вещества, такого как трихлорэтилен.

Удаление фоторезиста

Шаг 6 - травление: Пластина погружается в травильный раствор фтористоводородной кислоты, который удаляет оксид с участков, через которые должны распространяться легирующие примеси.

Травление SiO2

Шаг 7 - Удаление всего слоя фоторезиста: Вовремя процесс травления , те участки SiO2, которые защищены слоем фоторезиста, не подвергаются воздействию. Теперь маска из фоторезиста удаляется химическим растворителем (горячая H2SO4).

Удаление слоя фоторезиста

Шаг 8 - Формирование N-скважины: Примеси n-типа диффундируют в подложку p-типа через открытую область, образуя таким образом N-лунку.

Формирование N-колодца

Шаг 9 - Удаление SiO2: Слой SiO2 теперь удаляется плавиковой кислотой.

Удаление SiO2

Шаг 10 - Нанесение поликремния: Несоосность ворот CMOS транзистор приведет к возникновению нежелательной емкости, которая может повредить цепь. Таким образом, чтобы предотвратить этот «процесс самовыравнивания затвора» предпочтителен, когда области затвора формируются до формирования истока и стока с использованием ионной имплантации.

Осаждение поликремния

Поликремний используется для изготовления затвора, так как он выдерживает высокие температуры выше 8000 ° С.0c, когда пластина подвергается методам отжига для образования истока и стока. Поликремний наносится с использованием Процесс химического осаждения поверх тонкого слоя оксида затвора. Этот тонкий оксид затвора под слоем поликремния предотвращает дальнейшее легирование под областью затвора.

Шаг 11 - Формирование области ворот: За исключением двух областей, необходимых для формирования ворот для NMOS и PMOS транзисторы оставшаяся часть поликремния удаляется.

Формирование области ворот

Шаг 12 - Процесс окисления: На пластину нанесен оксидный слой, который действует как экран для дальнейшего процессы диффузии и металлизации .

Процесс окисления

Шаг 13 - Маскирование и диффузия: Для создания областей диффузии примесей n-типа методом маскировки делаются небольшие зазоры.

Маскировка

Используя процесс диффузии, создаются три области n + для образования концов NMOS.

N-диффузия

Шаг 14 - Удаление оксида: Оксидный слой удаляется.

Удаление оксида

Шаг 15 - Диффузия P-типа: Аналогично диффузии n-типа для формирования терминалов PMOS осуществляется диффузия p-типа.

Диффузия P-типа

Шаг 16 - Укладка оксида толстого поля: Перед формированием металлических выводов наносится толстопольный оксид, чтобы сформировать защитный слой для областей пластины, где выводы не требуются.

Толстый оксидный слой поля

Шаг 17 - Металлизация: Этот шаг используется для формирования металлических клемм, которые могут обеспечивать межсоединения. Алюминий нанесен на всю пластину.

Металлизация

Шаг 18 - Удаление лишнего металла: Излишки металла удаляются с пластины.

Шаг 19 - Формирование терминалов: В промежутках, образовавшихся после удаления излишков металла, образуются клеммы для межсоединений.

Формирование терминалов

Шаг 20 - Назначение имен терминалов: Названия присвоены терминалам NMOS и PMOS транзисторы .

Назначение имен терминалов

Изготовление CMOS по технологии P well

Процесс с p-лунками аналогичен процессу с N-лунками, за исключением того, что здесь используется подложка n-типа и выполняется диффузия p-типа. Для простоты обычно предпочтительнее N скважинный процесс.

Изготовление двухтрубной КМОП-матрицы

Используя двухтрубный процесс, можно управлять усилением устройств P- и N-типа. Различные этапы, связанные с изготовление CMOS с использованием метода двойной трубки являются следующими

- Берется слабо легированная подложка n- или p-типа и используется эпитаксиальный слой. Эпитаксиальный слой защищает микросхему от защелкивания.

- Выращиваются слои кремния высокой чистоты с измеренной толщиной и точной концентрацией легирующей примеси.

- Формирование трубок для скважины P и N.

- Тонкая оксидная конструкция для защиты от загрязнения во время диффузионных процессов.

- Исток и сток сформированы методами ионной имплантации.

- Сделаны вырезы для изготовления участков под металлические контакты.

- Металлизация сделана под вытяжку металлических контактов.

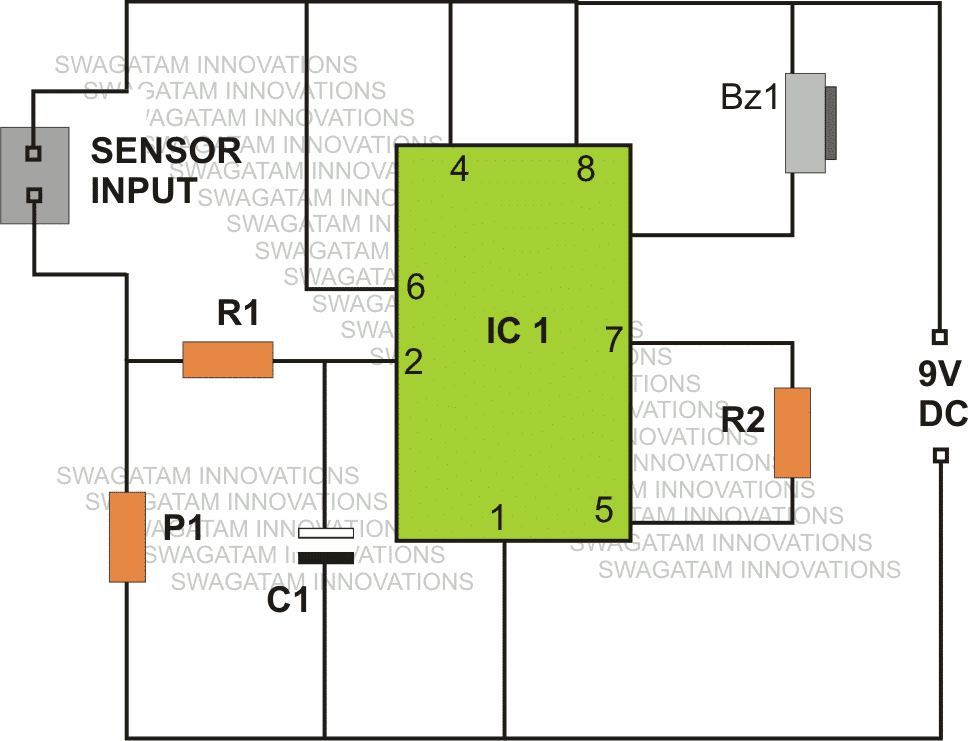

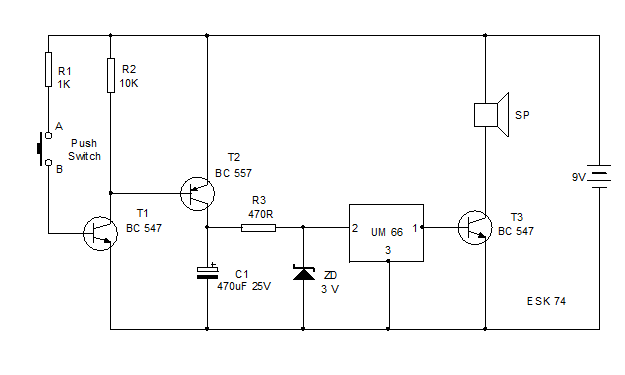

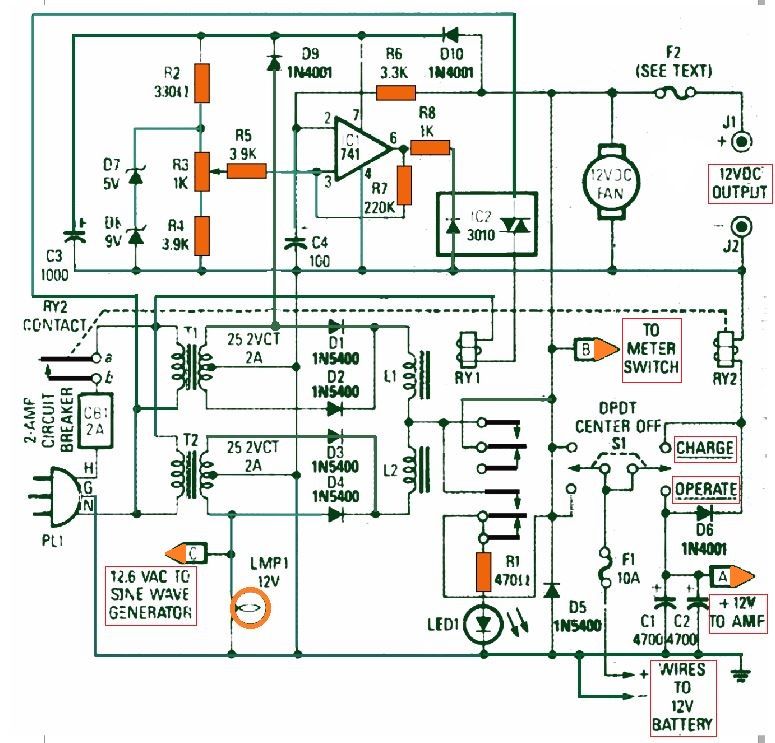

Схема CMOS IC

Вид сверху в CMOS изготовление и макет дано. Здесь отчетливо видны различные металлические контакты и диффузии с N ямами.

Схема CMOS IC

Таким образом, это все о Методы изготовления CMOS . Давайте рассмотрим пластину размером 1 квадрат, разделенную на 400 чипов с площадью поверхности 50 мил на 50 мил. Для изготовления транзистора требуется площадь 50 мил2. Следовательно, каждая ИС содержит 2 транзистора, поэтому на каждой пластине построено 2 x 400 = 800 транзисторов. Если в каждой партии обрабатывать 10 пластин, то одновременно можно производить 8000 транзисторов. Какие компоненты вы наблюдали на ИС?