В цифровая электроника добавление двухбитовых двоичных чисел возможно с помощью полусумматор . А если входная последовательность имеет трехбитовую последовательность, то процесс сложения может быть завершен с использованием полного сумматора. Но если количество битов во входной последовательности больше, процесс может быть завершен с помощью полусумматора. Потому что полный сумматор не может завершить операцию сложения. Таким образом, эти недостатки можно преодолеть с помощью «Ripple Carry Adder». Это уникальный тип логическая схема используется для сложения N-битных чисел в цифровых операциях. В этой статье описывается обзор того, что такое сумматор с переносом пульсации и его работа.

Что такое Ripple Carry Adder?

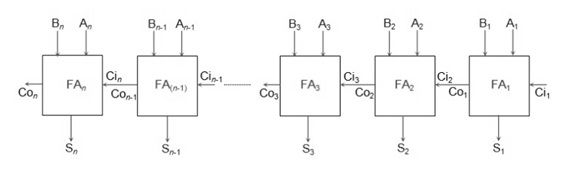

Структура из нескольких полных сумматоров каскадируется таким образом, чтобы получить результаты сложения n-битной двоичной последовательности. Этот сумматор включает в себя каскадные полные сумматоры в своей структуре, поэтому перенос будет генерироваться на каждом этапе полного сумматора в цепи сумматора с волновым переносом. Эти выходные данные переноса на каждом каскаде полного сумматора перенаправляются на его следующий полный сумматор и там применяются в качестве входного сигнала переноса. Этот процесс продолжается до последней стадии полного суммирования. Таким образом, каждый выходной бит переноса передается на следующий этап полного сумматора. По этой причине он называется «RIPPLE CARRY ADDER». Наиболее важной особенностью этого является добавление входных битовых последовательностей, независимо от того, является ли последовательность 4-битной, 5-битной или любой другой.

«Один из наиболее важных моментов, который следует учитывать в этом сумматоре переноса, заключается в том, что окончательный результат становится известен только после того, как выходные данные переноса генерируются каждым каскадом полного сумматора и направляются на его следующий этап. Так что при использовании сумматора переноса будет задержка в получении результата ».

Существуют различные типы сумматоров с волновым переносом. Они есть:

- 4-битный сумматор с переносом пульсации

- 8-битный сумматор с переносом пульсации

- 16-битный сумматор с переносом пульсации

Сначала мы начнем с 4-битного сумматора с переносом пульсации, а затем с 8-битного и 16-разрядного сумматора с переносом пульсации.

4-битный сумматор переноса пульсации

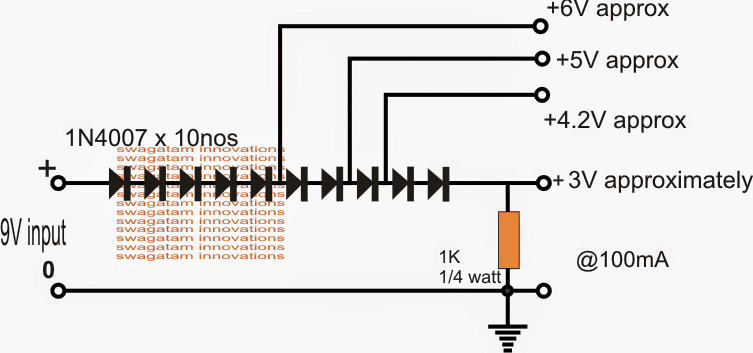

На схеме ниже представлен 4-битный сумматор с переносом пульсации. В этом сумматоре четыре полных сумматора соединены каскадом. Co - это входной бит переноса, и он всегда равен нулю. Когда этот входной перенос «Co» применяется к двум входным последовательностям A1 A2 A3 A4 и B1 B2 B3 B4, тогда выходной перенос представлен как S1 S2 S3 S4 и выходной перенос C4.

4-битная схема RCA

Работа 4-битного сумматора Ripple Carry

- Давайте рассмотрим пример двух входных последовательностей 0101 и 1010. Они представляют A4 A3 A2 A1 и B4 B3 B2 B1.

- Согласно этой концепции сумматора, входной перенос равен 0.

- Когда Ao и Bo применяются к 1-му полному сумматору вместе с входным переносом 0.

- Здесь A1 = 1 B1 = 0 Cin = 0

- Сумма (S1) и перенос (C1) будут генерироваться в соответствии с уравнениями суммы и переноса этого сумматора. Согласно его теории, выходное уравнение для Sum = A1⊕B1⊕Cin и Carry = A1B1⊕B1Cin⊕CinA1

- Согласно этому уравнению, для 1-го полного сумматора S1 = 1 и выход переноса, т.е. C1 = 0.

- То же, что и для следующих входных битов A2 и B2, выход S2 = 1 и C2 = 0. Здесь важным моментом является то, что полный сумматор второй ступени получает входной перенос, то есть C1, который является выходным переносом полного сумматора начальной ступени.

- Таким образом получится окончательная выходная последовательность (S4 S3 S2 S1) = (1 1 1 1) и выходной перенос C4 = 0

- Это процесс сложения для 4-битных входных последовательностей, когда он применяется к сумматору переноса.

8-битный сумматор Ripple Carry

- Он состоит из 8 полных сумматоров, которые соединены каскадом.

- Каждый выход переноса полного сумматора подключается как входной перенос к полному сумматору следующего каскада.

- Входные последовательности обозначены (A1 A2 A3 A4 A5 A6 A7 A8) и (B1 B2 B3 B4 B5 B6 B7 B8), а соответствующая выходная последовательность обозначена (S1 S2 S3 S4 S5 S6 S7 S8).

- Процесс сложения в 8-битном сумматоре с пульсационным переносом - это тот же принцип, который используется в 4-битном сумматоре с пульсационным переносом, то есть каждый бит из двух входных последовательностей будет добавлен вместе с входным переносом.

- Это будет использоваться при сложении двух 8-битных двоичных цифр последовательности.

8-битный сумматор

16-битный сумматор переноса пульсации

- Он состоит из 16 полных сумматоров, которые соединены каскадом.

- Каждый выход переноса полного сумматора подключается как входной перенос к полному сумматору следующего каскада.

- Входные последовательности обозначены (A1… .. A16) и (B1 …… B16), а соответствующая выходная последовательность обозначена (S1 …… .. S16).

- Процесс сложения в 16-битном сумматоре с пульсационным переносом - тот же принцип, который используется в 4-битном сумматоре с пульсационным переносом, то есть каждый бит из двух входных последовательностей будет добавляться вместе с входным переносом.

- Это будет использоваться при сложении двух 16-битных двоичных цифр последовательности.

16-битный сумматор с переносом пульсации

Таблица истинности Ripple Carry Adder

В приведенной ниже таблице истинности показаны выходные значения для возможных комбинаций всех входов для сумматора с переносом пульсации.

| A1 | A2 | A3 | A4 | B4 | B3 | Би 2 | B1 | S4 | S3 | S2 | S1 | Нести |

0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

Код VHDL Ripple Carry Adder

VHDL (VHSIC HDL) - язык описания оборудования. Это язык цифрового дизайна. Код VHDL для этого сумматора переноса показан ниже.

библиотека IEEE

используйте IEEE.STD_LOGIC_1164.ALL

сущность Ripplecarryadder является

Порт (A: в STD_LOGIC_VECTOR (от 3 до 0)

B: в STD_LOGIC_VECTOR (от 3 до 0)

Cin: в STD_LOGIC

S: из STD_LOGIC_VECTOR (от 3 до 0)

Cout: из STD_LOGIC)

конец Ripplecarryadder

архитектура Поведение Ripplecarryadder - полное объявление компонента кода VHDL Adder

компонент full_adder_vhdl_code

Порт (A: в STD_LOGIC

B: в STD_LOGIC

Cin: в STD_LOGIC

S: из STD_LOGIC

Cout: из STD_LOGIC)

конечный компонент

- Декларация о промежуточном перевозке

Сигнал c1, c2, c3: STD_LOGIC

начинать

- Port Mapping Full Adder 4 раза

FA1: карта портов full_adder_vhdl_code (A (0), B (0), Cin, S (0), c1)

FA2: карта портов full_adder_vhdl_code (A (1), B (1), c1, S (1), c2)

FA3: карта портов full_adder_vhdl_code (A (2), B (2), c2, S (2), c3)

FA4: карта портов full_adder_vhdl_code (A (3), B (3), c3, S (3), Cout)

конец Поведенческий

Код Verilog от Ripple Carry Adder

Код Verilog - это язык описания оборудования. Он используется в цифровых схемах на этапе RTL для целей проектирования и проверки. Код Verilog для этого сумматора переноса показан ниже.

модуль ripple_carry_adder (a, b, cin, sum, cout)

ввод [03: 0] а

ввод [03: 0] b

вход cin

выход [03: 0] сумма

выход cout

провод [2: 0] c

fulladd a1 (a [0], b [0], cin, sum [0], c [0])

fulladd a2 (a [1], b [1], c [0], sum [1], c [1])

fulladd a3 (a [2], b [2], c [1], sum [2], c [2])

fulladd a4 (a [3], b [3], c [2], sum [3], cout)

конечный модуль

fulladd модуль (а, б, КИН, сумма, соиЬ)

введите a, b, cin

выходная сумма, cout

назначить сумму = (a ^ b ^ cin)

назначить cout = ((a & b) | (b & cin) | (a & cin))

Приложения Ripple Carry Adder

К приложениям сумматора с переносом пульсации относятся следующие.

- Эти сумматоры переноса используются в основном в дополнение к n-битным входным последовательностям.

- Эти сумматоры переноса применимы в цифровой обработке сигналов и микропроцессоры .

Преимущества Ripple Carry Adder

К преимуществам сумматора с переносом пульсаций можно отнести следующее.

- У этого сумматора переноса есть то преимущество, что мы можем выполнять процесс сложения для n-битных последовательностей, чтобы получить точные результаты.

- Создание сумматора - несложный процесс.

Сумматор переноса пульсации является альтернативой, когда полусумматор и полные сумматоры не выполняют операцию сложения при больших входных битовых последовательностях. Но здесь он выдаст выход для любых входных битовых последовательностей с некоторой задержкой. В соответствии с цифровыми схемами, если схема выдает выходной сигнал с задержкой, это не будет предпочтительным. Это может быть преодолено схемой сумматора с упреждающим переносом.