Как правило, полный вычитатель является одним из наиболее часто используемых и основные схемы комбинационной логики . Это базовое электронное устройство, используемое для вычитания двух двоичных чисел. В предыдущей статье мы уже изложили основную теорию полусумматор и полный сумматор который использует двоичные цифры для вычислений. Точно так же полный вычитатель использует двоичные цифры, например 0,1, для вычитания. Схема этого может быть построена с логическими вентилями, такими как вентиль OR, Ex-OR, логический элемент NAND. Входы этого вычитателя - A, B, Bin, а выходы - D, Bout.

Эта статья дает идею теории полного вычитания, которая включает в себя такие предпосылки, как вычитатель, дизайн с логическими воротами, таблица истинности и т. Д. Эта статья полезна для студентов инженерных специальностей, которые могут пройти эти темы в практической лаборатории HDL.

Что такое вычитатель?

Вычитание двоичных разрядов можно производить с помощью схемы вычитателя. Это один из видов комбинационной логической схемы, используемый для вычитания двух двоичных цифр, таких как 0 и 1. Вычитание двоичных цифр от 0 до 0 или от 0 до 1 не изменяет результат, вычитание от 1 до 1 приведет к 0, но вычитание от 1 до 0 требует заимствования.

Например, двухбитовая схема вычитания включает два входа, такие как A и B, тогда как выходы разностные и заимствованные. Эта схема может быть построена с сумматорами вместе с инверторами, которые расположены между каждым входом данных, а также входом заимствования (Bin) более ранней фазы FA.

Вычитатели делятся на два типа, например, половинный вычитатель и полный вычитатель. Здесь мы обсуждаем полный вычитатель.

Что такое полный вычитатель?

Это электронное устройство или логическая схема который выполняет вычитание двух двоичных цифр. Это комбинационная логическая схема, используемая в цифровой электронике. Многие комбинационные схемы доступны в технология интегральных схем а именно сумматоры, кодеры, декодеры и мультиплексоры. В этой статье мы собираемся обсудить его построение с использованием половинного вычитателя, а также такие термины, как таблица истинности.

Полный вычитатель

Проектирование этого может быть выполнено двумя половинными вычитателями, которые включают три входа, такие как уменьшение, вычитание и заимствование, бит заимствования среди входов получается вычитанием двух двоичных цифр и вычитается из следующей пары более высокого порядка биты, выходы как разность и заимствования.

В полная блок-схема вычитателя показано ниже. Главный недостаток половинного вычитателя заключается в том, что мы не можем сделать бит заимствования в этом вычитателе. Принимая во внимание, что в его конструкции, на самом деле мы можем сделать бит заимствования в схеме и можем вычесть из оставшихся двух i / ps. Здесь A - вычитаемое, B - вычитаемое, а Bin - заимствованное. Выходы - это разница (Diff) и Bout (заимствовать). Полная схема вычитателя может быть получена с помощью двух половинных вычитателей с дополнительным вентилем ИЛИ.

Полная принципиальная схема вычитателя с логическими вентилями

В принципиальная схема полного вычитателя с использованием основного гейта s показан на следующей блок-схеме. Эта схема может быть выполнена с помощью двух схем полувычитателя.

В исходной схеме полувычитателя двоичными входами являются A и B. Как мы обсуждали в предыдущей статье о полувычитателе, он будет генерировать два выхода, а именно разность (Diff) и заимствование.

Полный вычитатель с использованием логических ворот

Разница o / p левого вычитателя передается на схему левого полувычитателя. Выход Diff дополнительно подается на вход схемы вычитателя правой половины. Мы предложили заимствовать бит через другой i / p следующего схема половинного вычитателя . Еще раз он выдаст Diff, а также Borrow out the bit. Конечный результат этого вычитателя - Diff-output.

С другой стороны, заимствование из обеих схем половинного вычитателя подключено к логическому вентилю ИЛИ. Позже, чем выдача логики ИЛИ для двух выходных битов вычитателя, мы получаем окончательную заимствование из вычитателя. Последний заимствованный для обозначения MSB (старший бит).

Если мы рассмотрим внутреннюю схему этого, мы увидим два полувычитателя с логическим элементом И-НЕ и вентиль XOR с дополнительным вентилем ИЛИ.

Полная таблица истинности вычитателя

Этот схема вычитателя выполняет вычитание между двумя битами, имеющими 3 входа (A, B и Bin) и два выхода (D и Bout). Здесь входы обозначают уменьшение, вычитание и предыдущее заимствование, тогда как два выхода обозначаются как заимствование o / p и разность. На следующем изображении показана таблица истинности полного вычитателя.

Входы | Выходы | |||

Минуэнд (А) | Вычесть (B) | Заимствовать (корзина) | Разница (D) | Заимствовать (Бут) |

0 | 0 | 0 | 0 | 0 |

0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

1 | 1 | 0 | 0 | 0 |

1 | 1 | 1 | 1 | 1 |

K-карта

Упрощение K-карта полного вычитателя для указанной выше разницы и заимствования показано ниже.

Уравнения для разности, а также Bin указаны ниже.

Выражение для Различия:

D = A’B’Bin + AB’Bin ’+ A’BBin’ + ABBin

Выражение для заимствования:

Бут = A’Bin + A’B + BBin

Каскадирование полной схемы вычитания

Ранее мы обсуждали обзор такой конструкции, принципиальной схемы с логическими вентилями. Но если мы хотим вычесть два, иначе больше 1-битных чисел, эта схема вычитания очень полезна для каскадирования одноразрядных чисел, а также для вычитания более двух двоичных чисел. В таких случаях используется полная каскадная схема сумматора с помощью логического элемента НЕ. Преобразование схемы из полного сумматора в полный вычитатель может быть выполнено с использованием техники дополнения до 2.

Как правило, инвертируйте входы вычитания для полного сумматора, используя вентиль НЕ, иначе инвертор. Добавляя Minuend (неинвертированный вход) и Subtrahend (инвертированный вход), LSB (вход переноса) схемы FA равен 1, что означает высокий логический уровень, в противном случае мы вычитаем две двоичные цифры, используя метод дополнения до 2. Выходной сигнал FA - это бит Diff, и если мы инвертируем выполнение, мы можем получить MSB, в противном случае - бит заимствования. Фактически, мы можем спроектировать схему так, чтобы можно было наблюдать за выходом.

Код Verilog

Для части кодирования, во-первых, нам нужно проверить структурный способ моделирования логической схемы. Логическая схема этого может быть построена с использованием логических элементов И, схем половинного вычитания и комбинации логических элементов, таких как И, ИЛИ, НЕ, ИЛИ. Как и в структурном моделировании, мы объясняем различные модули для каждого базового расположения элементов. В следующем коде для каждого гейта можно определить разные модули.

Этот модуль предназначен для ворот ИЛИ.

ВХОД: a0, b0

ВЫХОД: c0

Наконец, мы объединим эти модули точных ворот в единственный модуль. Для этого здесь мы используем экземпляр модуля. Теперь этот экземпляр можно использовать, если мы хотим воспроизвести точный модуль или функцию для различных входных наборов. Сначала мы проектируем половинный вычитатель, затем этот модуль используется для реализации полного вычитателя. Для реализации этого мы используем логический элемент OR, чтобы объединить o / ps для переменной Bout. В код verilog для полного вычитателя показано ниже

модуль or_gate (a0, b0, c0)

вход a0, b0

выход c0

присвоить c0 = a0 | b0

конечный модуль

модуль xor_gate (a1, b1, c1)

вход a1, b1

выход c1

назначить c1 = a1 ^ b1

конечный модуль

модуль and_gate (a2, b2, c2)

вход a2, b2

выход c2

назначить c2 = a2 & b2

конечный модуль

модуль not_gate (a3, b3)

вход a3

выход b3

назначить b3 = ~ a3

конечный модуль

модуль half_subtractor (a4, b4, c4, d4)

вход a4, b4

выход c4, d4

провод x

xor_gate u1 (a4, b4, c4)

and_gate u2 (x, b4, d4)

not_gate u3 (a4, x)

конечный модуль

модуль full_subtractor (A, B, Bin, D, Bout)

вход A, B, Bin

выход D, Bout

проволока p, q, r

половинный вычитатель u4 (A, B, p, q)

половинный вычитатель u5 (p, Bin, D, r)

or_gate u6 (q, r, Бут)

конечный модуль

Полный вычитатель с использованием мультиплексора 4X1

Вычитание может быть выполнено с помощью метода дополнения до двух. Таким образом, нам необходимо использовать вентиль 1-XOR, который используется для инвертирования 1 бита и включения его в бит переноса. Выход DIFFERENCE аналогичен выходному SUM в схеме полного сумматора, однако BARROW o / p не похож на выход переноса полного сумматора, однако он инвертируется, а также дополняется, например A - B = A + (-B) = A + два дополнения к B.

Его конструкция с использованием мультиплексора 4X1 показана на следующей логической схеме. Этот дизайн можно сделать, выполнив следующие шаги.

Мультиплексор 4X1

- На шаге 1 есть два выхода, такие как Sub и Borrow. Итак, нам нужно выбрать 2 мультиплексора.

- На шаге 2 таблица истинности может быть реализована вместе с K-картами

- На шаге 3 две переменные могут быть выбраны в качестве строки выбора. Например, B & C в этом случае.

Таблица правды

В таблица истинности полного вычитателя Схема с использованием мультиплексора 4X1 включает в себя следующие

К | B | C | Sub | Поручительство |

0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

1 | 1 | 1 | 1 | 1 |

Полный вычитатель с использованием декодера

Создание полного вычитателя с использованием 3-8 декодеров может быть выполнено с использованием активных низких выходов. Предположим, что декодер функционирует по следующей логической схеме. Декодер включает три входа в 3-8 декодеров. Основываясь на таблице истинности, мы можем написать minterms для выходов разницы и заимствования.

Из приведенной выше таблицы истинности

Для различных функций в таблице истинности минтермы могут быть записаны как 1, 2, 4, 7, и аналогично, для заимствований, минтермы могут быть записаны как 1,2,3,7. Декодеры 3-8 включают три входа, а также 8 выходов от lik0 до 7 чисел.

Декодер от 3 до 8

Если на входе вычитателя 000, то будет активен выход «0», а если на входе 001, то будет активен выход «1».

Теперь выходы вычитателя можно взять из 1, 2, 4 и 7, чтобы подключить его к логическому элементу И-НЕ, тогда выход будет разницей. Эти выходы могут быть подключены к другим логическим элементам NAND, где выход изменяется на заимствование.

Например, если на входе 001, то на выходе будет 1, что означает, что он активен. Таким образом, на выходе активен низкий уровень, и выходной сигнал может быть получен из логического элемента И-НЕ, называемого функцией разности, например, high, и функция заимствования также меняется на высокое. Таким образом, мы получаем желаемый результат. Итак, наконец, декодер работает как полный вычитатель.

Преимущества и недостатки

В преимущества вычитателя включая следующее.

- Конструкция вычитателя очень проста.

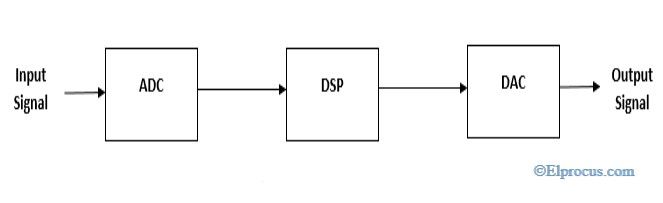

- Удержание мощности в DSP (цифровая обработка сигналов)

- Вычислительные задачи могут выполняться с высокой скоростью.

В Недостатки вычитателя включая следующее.

- В половинном вычитателе нет условий для принятия заимствованных входных данных из более ранней фазы.

- Скорость вычитателя может быть частичной из-за задержки в цепи.

Приложения

Несколько из заявки полного вычитателя включая следующее

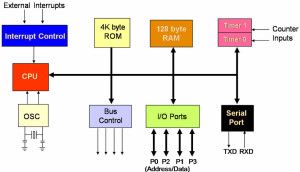

- Они обычно используются для ALU (арифметического логического блока) в компьютерах, чтобы вычесть ЦП и ГП для графических приложений, чтобы уменьшить сложность схемы.

- Вычитатели в основном используются для выполнения арифметических функций, таких как вычитание, в электронных калькуляторах, а также в цифровых устройствах.

- Они также применимы для разные микроконтроллеры для арифметического вычитания, таймеры и счетчик программ (ПК)

- Вычитатели используются в процессорах для вычисления таблиц, адресов и т. Д.

- Это также полезно для DSP и сетевых систем.

- Они используются в основном для ALU в компьютерах для вычитания, например, CPU и GPU для графических приложений, чтобы уменьшить сложность схемы.

- Они в основном используются для выполнения арифметических функций, таких как вычитание в цифровых устройствах, калькуляторах и т. Д.

- Эти вычитатели также подходят для различных микроконтроллеров для таймеров, ПК (счетчик программ) и арифметического вычитания.

- Они используются процессорами для вычисления адресов, таблиц и т. Д.

- Реализация этого с помощью логических вентилей, таких как И-НЕ и ИЛИ-ИЛИ, может быть выполнена с помощью любой полной логической схемы вычитателя, потому что и ИЛИ-И-И, и И-НЕ называются универсальными вентилями.

Из приведенной выше информации, оценивая сумматор, полный вычитатель с использованием двух схем половинного вычитателя и его табличную форму, можно заметить, что Dout в полном вычитателе точно аналогичен Sout полного сумматора. Единственная вариация состоит в том, что A (входная переменная) дополняется в полном вычитателе. Таким образом, возможно преобразовать схему полного сумматора в схему полного вычитания, просто дополнив i / p A перед тем, как он будет передан в логические ворота для генерации последнего бита заимствования (Bout).

Используя любую логическую схему полного вычитателя, можно реализовать полный вычитатель, использующий вентили NAND, и полный вычитатель, использующий вентили Nor, так как вентили NAND и NOR рассматриваются как универсальные вентили. Вот вам вопрос, в чем разница между половинным вычитателем и полным вычитателем?