В области электроники наиболее важной концепцией, над которой работает каждый компонент, является « Логические ворота «. Поскольку концепция логических вентилей реализована во всех функциях, таких как интегральные схемы, датчики, цели переключения, микроконтроллеры и процессоры, цели шифрования и дешифрования и другие. В дополнение к этому, есть широкое применение логических вентилей. Есть много типов логических вентилей, таких как сумматор, вычитатель, полный Сумматор , Полный вычитатель, Половинный вычитатель и многие другие. Итак, в этой статье собрана информация о схема половинного вычитателя , таблица истинности половинного вычитателя , и связанные концепции.

Что такое Half Subtractor?

Прежде чем перейти к обсуждению полувычитателя, мы должны знать двоичное вычитание. В двоичном вычитании процесс вычитания аналогичен арифметическому вычитанию. В арифметическом вычитании используется система счисления с основанием 2, тогда как в двоичном вычитании двоичные числа используются для вычитания. Полученные термины можно обозначить разницей и заимствовать.

Половинный вычитатель - самый важный комбинационная логическая схема который используется в цифровая электроника . По сути, это электронное устройство или, другими словами, можно сказать, что это логическая схема. Эта схема используется для вычитания двух двоичных цифр. В предыдущей статье мы уже обсуждали концепции полусумматора и полного сумматора который использует двоичные числа для расчета. Точно так же схема вычитателя использует двоичные числа (0,1) для вычитания. Схема полувычитателя может быть построена с двумя логические вентили, а именно вентили NAND и EX-OR . Эта схема дает два элемента, такие как разницу, а также их заимствования.

Как и в двоичном вычитании, старшая цифра равна 1, мы можем сгенерировать заимствование, в то время как вычитаемый 1 превосходит вычитаемый 0, и поэтому потребуется заимствование. В следующем примере показано двоичное вычитание двух двоичных разрядов.

Первая цифра | Вторая цифра | Разница | Поручительство |

0 | 0 | 0 | 0 |

1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

В приведенном выше вычитании две цифры могут быть представлены с помощью A и B. Эти две цифры могут быть вычтены и дают результирующие биты как разность и заимствование.

Когда мы наблюдаем первые две и четвертые строки, разницу между этими строками, тогда разница и заимствование аналогичны, потому что вычитаемое меньше, чем уменьшаемое. Точно так же, когда мы наблюдаем третью строку, уменьшенное значение вычитается из вычитаемого. Таким образом, биты разности и заимствования равны 1, потому что вычитаемая цифра превосходит уменьшаемую цифру.

Эта комбинационная схема - незаменимый инструмент для любого вида цифровая схема чтобы знать возможные комбинации входов и выходов. Например, если у вычитателя два входа, то результирующих выходов будет четыре. Значение o / p полувычитателя указано в таблице ниже, которая будет обозначать бит разности, а также бит заимствования. Объяснение таблицы истинности схемы может быть выполнено с использованием логических элементов, таких как логический элемент EX-OR и операция элемента AND, за которой следует элемент NOT.

Решение таблицы истинности с помощью K-карта показано ниже.

половина вычитателя k map

В выражение половинного вычитателя используя таблицу истинности и K-карту, можно получить как

Разница (D) = ( х'у + ху ')

знак равно х ⊕ у

Заимствовать (B) = x’y

Логическая схема

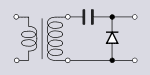

В логическая схема половинного вычитателя можно объяснить с помощью логических вентилей:

- 1 ворота XOR

- 1 НЕ ворота

- 1 И ворота

Представление

Логическая схема половинного вычитателя

Блок-схема полувычитателя

Блок-схема полувычитателя показана выше. Он требует двух входов, а также дает два выхода. Здесь входы обозначены буквами A&B, а выходами - разница и заимствование.

Вышеупомянутая схема может быть разработана с воротами EX-OR и NAND. Здесь вентиль И-НЕ может быть построен с использованием логических элементов И и НЕ. Таким образом, нам требуются три логических элемента для создания половины схемы вычитания, а именно элемент EX-OR, элемент НЕ и элемент И-НЕ.

Комбинация логических элементов И и НЕ создает другой комбинированный вентиль с именем И-НЕ. Выход логического элемента Ex-OR будет битом разности, а выход логического элемента И-НЕ будет битом заимствования для тех же входов A&B.

И-ворота

Логический элемент И - это один из типов цифровых логических элементов с несколькими входами и одним выходом, и на основе комбинаций входов он будет выполнять логическое соединение. Когда все входы этого затвора имеют высокий уровень, тогда выход будет высоким, в противном случае выход будет низким. Логическая схема логического элемента И с таблицей истинности показана ниже.

И ворота и таблица истины

НЕ ворота

НЕ-вентиль - это один из типов цифровых логических вентилей с одним входом, и в зависимости от входа выход будет реверсирован. Например, когда вход логического элемента НЕ высокий, выход будет низким. Логическая схема НЕ-гейта с таблицей истинности показана ниже. Используя этот тип логических вентилей, мы можем выполнять вентили И-НЕ и ИЛИ-ИЛИ.

НЕ ворота и таблица истины

Ex-OR Gate

Элемент «Исключающее ИЛИ» или «ИСКЛЮЧАЮЩЕЕ ИЛИ» - это один из типов цифровых логических элементов с 2 входами и одним выходом. Работа этого логического элемента зависит от логического элемента ИЛИ. Если на каком-либо из входов этого логического элемента высокий уровень, то выход элемента EX-OR будет высоким. Символы и таблица истинности EX-OR показаны ниже.

XOR Gate и таблица истинности

Схема половинного вычитателя с использованием Nand Gate

Проектирование вычитателя может быть выполнено используя логические вентили как ворота NAND и ворота Ex-OR. Чтобы спроектировать эту схему полувычитателя, мы должны знать две концепции, а именно разницу и заимствование.

Схема половинного вычитателя с использованием Nand Gate

Если мы будем внимательно следить за этим, становится довольно ясно, что разнообразие операций, выполняемых этой схемой, точно связано с операцией логического элемента EX-OR. Следовательно, мы можем просто использовать вентиль EX-OR, чтобы изменить ситуацию. Таким же образом, заимствование, производимое схемой полусумматора, может быть просто достигнуто путем использования комбинации логических элементов, таких как вентиль И и вентиль НЕ.

Этот HS также может быть спроектирован с использованием ворот NOR, где для строительства требуется 5 ворот NOR. Принципиальная схема полувычитателя, использующего вентили ИЛИ-НЕ, показана как:

Половинный вычитатель с использованием Нор Гейтса

Таблица правды

Первый бит | Второй бит | Разница (EX-OR) | Поручительство (NAND Out) |

0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

Код VHDL и Testbench

Код VHDL для половинного вычитателя объясняется следующим образом:

библиотека IEEE

используйте IEEE.STD_LOGIC_1164.ALL

используйте IEEE.STD_LOGIC_ARITH.ALL

используйте IEEE.STD_LOGIC_UNSIGNED.ALL

сущность Half_Sub1 является

Порт (a: в STD_LOGIC

b: в STD_LOGIC

HS_Diff: из STD_LOGIC

HS_Borrow: из STD_LOGIC)

конец Half_Sub1

архитектура Поведение Half_Sub1

начинать

HS_Diff<=a xor b

HS_Borrow<=(not a) and b

В тестовый код для HS объясняется ниже:

БИБЛИОТЕКА IEEE

ИСПОЛЬЗУЙТЕ ieee.std_logic_1164.ALL

ENTITY HS_tb IS

КОНЕЦ HS_tb

АРХИТЕКТУРА HS_tb OF HS_tb IS

КОМПОНЕНТ HS

ПОРТ (a: IN std_logic

b: IN std_logic

HS_Diff: OUT std_logic

HS_Borrow: OUT std_logic

)

КОНЕЧНЫЙ КОМПОНЕНТ

сигнал a: std_logic: = ‘0’

сигнал b: std_logic: = ‘0’

сигнал HS_Diff: std_logic

сигнал HS_Borrow: std_logic

НАЧИНАТЬ

новое: HS PORT MAP (

а => а,

б => б,

HS_Diff => HS_Diff,

HS_borrow => HS_borrow

)

стим_проц: процесс

начинать

к<= ‘0’

б<= ‘0’

подождите 30 нс

к<= ‘0’

б<= ‘1’

подождите 30 нс

к<= ‘1’

б<= ‘0’

подождите 30 нс

к<= ‘1’

б<= ‘1’

ждать

завершить процесс

КОНЕЦ

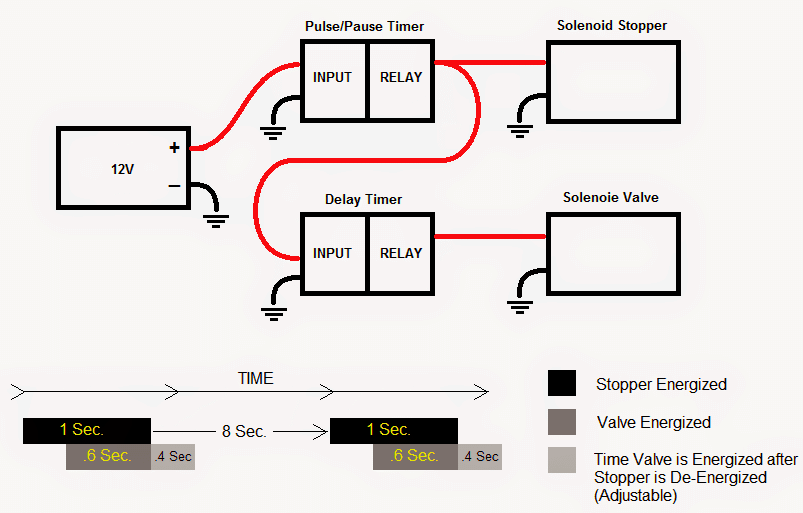

Полный вычитатель с использованием половинного вычитателя

Полный вычитатель - это комбинационное устройство, которое управляет функцией вычитания с помощью двух битов, а также уменьшает и вычитает. Схема рассматривает заимствование предыдущего выхода и имеет три входа с двумя выходами. Три входа - это minuend, subtrahend и вход, полученный из предыдущего выхода, который является заимствованием, а два выхода - это разница и заимствование.

Полная логическая схема вычитателя

Таблица истинности для полный вычитатель является

| Входы | Выходы | |||

| Икс | Y | Инь | FS_Diff | FS_Borrow |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

С приведенной выше таблицей истинности логическая диаграмма и схема схем для реализации полного вычитателя с использованием половинных вычитателей показаны ниже:

Полный вычитатель с использованием HS

Преимущества и ограничения полувычитателя

Преимущества полувычитателя:

- Реализация и конструкция этой схемы проста и удобна.

- Эта схема потребляет минимальную мощность при цифровой обработке сигналов.

- вычислительные функции могут выполняться с улучшенной скоростью

Ограничения этой комбинационной схемы:

Несмотря на то, что полувычитатель широко применяется во многих операциях и функциях, есть несколько ограничений, а именно:

- Цепи половинного вычитателя не принимают «заимствование» с предыдущих выходов, что является критическим недостатком этой схемы.

- Поскольку многие приложения реального времени работают с вычитанием большого количества битов, устройства половинного вычитания не имеют возможности вычитать большое количество битов.

Применение половинного вычитателя

Области применения полувычитателя включают следующее.

- Полувычитатель используется для уменьшения силы звуковых или радиосигналов.

- Может быть используется в усилителях уменьшить искажение звука

- Половина вычитателя используется в АЛУ процессора

- Может использоваться для увеличения и уменьшения операторов, а также для вычисления адресов.

- Половинный вычитатель используется для вычитания наименее значимых номеров столбцов. Для вычитания многозначных чисел его можно использовать для младшего разряда.

Таким образом, исходя из вышеупомянутой теории полувычитателя, мы, наконец, можем заключить, что с помощью этой схемы мы можем вычитать один двоичный бит из другого, чтобы получить такие выходные данные, как Разность и Заимствование. Точно так же мы можем спроектировать половинный вычитатель, используя схему вентилей И-НЕ, а также вентили ИЛИ-ИЛИ. Другие концепции, которые необходимо знать, - это то, что код Verilog половинного вычитателя а как можно нарисовать схему RTL?