В повседневной жизни мы сталкиваемся с различными типами электронных устройств. Одна из технологий, которая произвела революцию в производстве электроники, - это « Интегральная схема «. Эта технология уменьшила размер электронных продуктов за счет увеличения плотности логические ворота за чип. Сегодня у нас есть разные типы и конфигурации ИС. Наблюдая за происходящим, мы обнаруживаем, что некоторые ИС могут использоваться только для одного конкретного приложения, в то время как некоторые ИС можно перепрограммировать и использовать для различных приложений. Эти типы ИС называются ASIC. Но чем они отличаются? Как их перепрограммировать? Почему некоторые ИС нельзя перепрограммировать? Найдите ответы на эти вопросы.

Что такое ASIC (специализированная интегральная схема)?

Полная форма ASIC Специальная интегральная схема. Эти схемы зависят от конкретного приложения. индивидуально изготовленные ИС для конкретного приложения. Обычно они разрабатываются с корневого уровня в зависимости от требований конкретного приложения. Некоторые из основных примеры интегральных схем для конкретных приложений - это микросхемы, используемые в игрушках, микросхемы, используемые для взаимодействия памяти и микропроцессора и т. д. Эти микросхемы могут использоваться только для того приложения, для которого они предназначены. Предположительно, эти типы ИС предпочтительны только для тех продуктов, которые имеют большой тираж. Поскольку ASIC разрабатываются с самого начала, они имеют высокую стоимость и рекомендуются только для массового производства.

Основное преимущество ASIC - уменьшенный размер кристалла, поскольку большое количество функциональных блоков схемы построено на одном кристалле. Современные ASIC обычно включают 32-битную микропроцессор , блоки памяти, сетевые схемы и т. д. Такой тип ASIC известен как Система на чипе . С развитием производственных технологий и расширением исследований методов проектирования разрабатываются ASIC с различными уровнями настройки.

Типы ASIC

ASIC подразделяются на категории в зависимости от количества настроек, которые программист может выполнять на чипе.

Типы ASIC

Полный заказ

В этом типе конструкции все логические ячейки адаптированы для конкретного приложения. Разработчик должен специально сделать логические ячейки для схем. Все слои маски для соединения настраиваются. Таким образом, программист не может изменять соединения микросхемы, и при программировании он должен знать схему схемы.

Один из лучших примеров полностью настраиваемых ASIC - это микропроцессор. Этот тип настройки позволяет разработчикам создавать различные аналоговые схемы, оптимизированные ячейки памяти или механические структуры на одной ИС. Этот ASIC является дорогостоящим и требует очень много времени на изготовление и проектирование. На разработку этих ИС уходит около восьми недель.

Обычно они предназначены для приложений высокого уровня. Максимальная производительность, минимальная площадь и высочайшая степень гибкости - основные характеристики полностью индивидуализированной конструкции. В конце концов, риск высок при проектировании, поскольку используемые логические элементы, резисторы и т. Д. Не проходят предварительное тестирование.

Полу-пользовательский

В этом типе дизайна логические ячейки берутся из стандартных библиотек. они не изготавливаются вручную, как в полностью нестандартном дизайне. Некоторые маски настраиваются, а некоторые взяты из предварительно созданной библиотеки. В зависимости от типа логических ячеек, взятых из библиотеки, и количества настроек, разрешенных для межсоединений, эти ASIC делятся на два типа - ASIC на основе стандартных ячеек и ASIC на основе шлюзового массива.

1). Стандартные ASIC на основе ячеек

Чтобы узнать эти ИС, сначала позвольте нам понять, что означает стандартная библиотека ячеек. Некоторые из логических ячеек, например И ворота, ИЛИ ворота , мультиплексоры, шлепки предварительно спроектированы дизайнерами с использованием различных конфигураций, стандартизированы и сохранены в виде библиотеки. Эта коллекция известна как стандартная библиотека ячеек.

ASIC на основе стандартных ячеек

В стандартных ячейках используются логические ячейки ASIC из этих стандартных библиотек. На микросхеме ASIC стандартная область ячеек или гибкий блок состоят из стандартных ячеек, расположенных в виде рядов. Наряду с этими гибкими блоками на кристалле используются мегаячейки, такие как микроконтроллеры или даже микропроцессоры. Эти мегоячейки также известны как мегафункции, макросы системного уровня, фиксированные блоки, стандартные функциональные блоки.

На приведенном выше рисунке представлена ASIC со стандартной ячейкой с одной стандартной площадью ячейки и четырьмя фиксированными блоками. Слои маски настраиваются. Здесь дизайнер может разместить стандартные ячейки в любом месте на кристалле. Они также известны как C-BIC.

2). ASIC на основе массива ворот

Этот тип полу-кастомных ASIC предопределил транзисторы на кремниевой пластине. разработчик не может изменить размещение транзисторов на кристалле. Базовый массив - это предопределенный образец массива вентилей, а базовая ячейка - это наименьшая повторяющаяся ячейка базового массива.

Разработчик несет ответственность только за изменение взаимосвязи между транзисторами, используя первые несколько металлических слоев кристалла. Разработчик выбирает из библиотеки массивов ворот. Их часто называют Masked Gate Array. ASIC на основе массива ворот бывают трех типов. Это канальная вентильная матрица, бесканальная вентильная матрица и структурированная вентильная матрица.

а) .Массив с канализированными воротами

В этом типе вентильной матрицы между рядами транзисторов остается пространство для проводки. Они похожи на CBIC, поскольку остается пространство для межсоединений между блоками, но в каналированной вентильной матрице строки ячеек имеют фиксированную высоту, тогда как в CBIC это пространство можно регулировать.

Чаннелированный массив ворот

Некоторые из основных особенностей этой вентильной матрицы: в этой вентильной матрице для соединения используются заранее определенные промежутки между строками. Срок изготовления от двух дней до двух недель.

б). Массив ворот без канала

Не осталось свободного места для маршрутизации между рядами ячеек, как это видно в массиве канализированных вентилей. Здесь маршрутизация выполняется сверху ячеек вентильной матрицы, так как мы можем настроить соединение между металлом 1 и транзисторами. Для маршрутизации мы оставляем транзисторы, лежащие на пути маршрутизации, неиспользованными. Срок изготовления - около двух недель.

Массив ворот без канала

в). Структурированная вентильная матрица

Этот тип вентильной матрицы имеет встроенный блок вместе со строками вентильной матрицы, как показано выше. Структурированная вентильная матрица имеет более высокую эффективность по площади, чем CBIC. Как и массив затворов с маской, они имеют более низкую стоимость и более быстрое выполнение работ. Здесь фиксированный размер встроенной функции накладывает ограничение на структурированный вентильный массив. Например, этот массив вентилей содержит область, зарезервированную для 32-битного контроллера, но если в приложении нам требуется только область для 16-битного контроллера, оставшаяся область будет потрачена впустую. Весь массив вентилей имеет время обработки от двух дней до двух недель и все имеют индивидуальные межсоединения.

Структурированная вентильная матрица

Программируемый ASIC

Есть два типа программируемых ASIC. Это PLD и FPGA

PLD (программируемые логические устройства)

Это стандартные легко доступные ячейки. Мы можем запрограммировать PLD для настройки части приложения, чтобы они считались ASIC. Мы можем использовать различные методы и программное обеспечение для программирования PLD. Они содержат обычную матрицу логических ячеек, обычно программируемую логику массива, а также триггеры или защелки. Здесь межкомпонентные соединения представлены как единый большой блок.

PROM является типичным примером этой IC. EPROM использует МОП-транзисторы в качестве межсоединения, поэтому, подавая высокое напряжение, мы можем его запрограммировать. PLD не имеют настраиваемых логических ячеек или межсоединений. У них быстрая обработка дизайна.

Программируемые логические устройства

ПЛИС (программируемая вентильная матрица)

Где PLD имеют программируемую логику массива в виде логических ячеек FPGA имеет структуру, подобную решетке ворот. PLD меньше и менее сложны, чем FPGA. Благодаря своей гибкости и характеристикам FPGA заменяет TTL в микроэлектронных системах. Срок выполнения дизайна составляет всего несколько часов.

Программируемая вентильная матрица

Ядро состоит из программируемых базовых логических ячеек, которые могут выполнять как комбинационные и последовательная логика . Мы можем программировать логические ячейки и соединяться между собой, используя некоторые методы. Базовые логические ячейки окружены матрицей программируемых межсоединений, а ядро окружено программируемыми ячейками ввода / вывода.

FPGA обычно состоит из конфигурируемых логических блоков, конфигурируемых блоков ввода-вывода, программируемых межсоединений, схемы синхронизации, ALU, памяти, декодеров.

Мы видели различные доступные типы ASIC. Теперь давайте разберемся, когда все эти настройки и соединения выполнены во время производства.

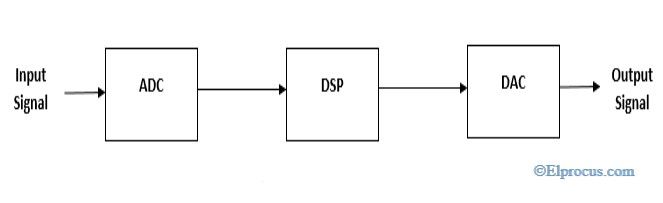

Схема проектирования интегральных схем для конкретных приложений (ASIC)

Разработка ASIC выполняется поэтапно. Этот порядок шагов известен как Дизайн ASIC Поток. Этапы процесса проектирования представлены на схеме ниже.

Схема проектирования ASIC

Вступление в дизайн: На этом этапе микроархитектура проекта реализуется с использованием таких языков описания оборудования, как VHDL, Verilog и System Verilog.

Логический синтез: На этом этапе с помощью HDL подготавливается список соединений логических ячеек, которые будут использоваться, типы соединений и все другие части, необходимые для приложения.

Системное разбиение: На этом этапе мы разделяем кристалл большого размера на части размером с ASIC.

Предварительное моделирование: На этом этапе проводится имитационный тест, чтобы проверить, нет ли в проекте ошибок.

Планировка этажа: На этом этапе на микросхеме размещаются блоки списка соединений.

Размещение: На этом этапе определяется расположение ячеек внутри блока.

Маршрутизация: На этом этапе проводятся связи между блоками и ячейками. Извлечение: на этом этапе мы определяем электрические свойства, такие как значение сопротивления и значение емкости межсоединения.

Пост-макетное моделирование: Перед отправкой модели для производства это моделирование выполняется, чтобы проверить, правильно ли функционирует система вместе с нагрузкой межсоединений.

Примеры ASIC

Теперь, зная различные характеристики ASIC, давайте рассмотрим несколько примеров ASIC.

Стандартные ASIC на основе ячеек: LCB 300k, 500k от LSI Logic Company, семейства SIG1, 2, 3 от ABB Hafo Inc., GCS90K от GCS Plessey.

Продукция для воротного массива: AUA20K от Harris Semiconductor, SCX6Bxx от National Semiconductors, семейства TGC / TEC от Texas Instruments.

Продукты PLD: Семейство PAL Advanced Micro Devices, семейство GAL от Philips Semiconductors, XC7300 и EPLD от XILINX.

Продукты FPGA: Серии XC2000, XC3000, XC4000, XC5000 от XILINX, pASIC1 от QuickLogic, MAX5000 от Altera.

Приложения ASIC

Уникальность ASIC произвела революцию в способах производства электроники. Это уменьшило размеры штампа при увеличении плотности логические ворота за чип. ASIC обычно предпочтительнее для приложений высокого уровня. Чип ASIC используется в качестве IP-ядер для спутников, изготовления ПЗУ, Микроконтроллер и различные типы приложений в медицинской и исследовательской сферах. Одно из самых популярных приложений ASIC - BITCOIN MINER.

Биткойн Майнер

Майнинг криптовалюты требует большей мощности и высокоскоростного оборудования. ЦП общего назначения не может обеспечить такую большую вычислительную мощность на высокой скорости. Биткойн-майнеры ASIC - это чипы, встроенные в специально разработанные материнские платы и Источники питания , построенный в единый блок. Это специально разработанное оборудование вплоть до уровня чипа для майнинга биткойнов. Эти единицы могут выполнять алгоритм только одной криптовалюты. Предположительно для другого типа криптовалюты нам потребуется еще один майнер.

Преимущества и недостатки ASIC

В преимущества ASIC включая следующее.

- Небольшой размер ASIC делает его отличным выбором для сложных более крупных систем.

- Поскольку большое количество схем построено на одном кристалле, это вызывает высокоскоростные приложения.

- ASIC имеет низкое энергопотребление.

- Поскольку они представляют собой систему на кристалле, схемы присутствуют рядом. Таким образом, для соединения различных цепей требуется минимальная маршрутизация.

- У ASIC нет проблем с синхронизацией и постпроизводственной конфигурацией.

В недостатки ASIC включая следующее.

- Поскольку это индивидуальные микросхемы, они обеспечивают низкую гибкость программирования.

- Поскольку эти микросхемы должны разрабатываться с самого начала, они имеют высокую стоимость за единицу.

- У ASIC больше времени выхода на рынок.

ASIC против FPGA

Разница между ASIC и FPGA заключается в следующем.

ASIC | FPGA |

| Не перепрограммируемый | Перепрограммируемый |

| Предпочтительно для крупносерийного производства | Предпочтительно для небольших объемов производства |

| Это зависит от приложения | Используется как прототип системы |

| Энергоэффективность требует меньше энергии | Менее энергоэффективное требует больше энергии |

| Это постоянные схемы, которые нельзя время от времени модернизировать. | Идеально подходит для приложений, в которых необходимо время от времени обновлять схему, например, для микросхем сотовых телефонов, базовых станций и т. Д. |

Таким образом, речь идет об обзоре Интегральная схема для конкретного приложения . Изобретение ASIC привело к огромным изменениям в способах использования электроники. Мы используем ASIC в повседневной жизни в виде различных приложений. С какими приложениями ASIC вы сталкивались? С каким типом ASIC вы работали?