Набор команд или архитектура набора команд - это структура компьютера, которая выдает команды компьютеру, чтобы направлять компьютер для обработки манипуляций с данными. Набор команд состоит из инструкций, режимов адресации, собственных типов данных, регистров, прерывания, обработки исключений и архитектуры памяти. Набор инструкций можно эмулировать программно с помощью интерпретатора или встроить в аппаратную часть процессора. Архитектуру набора команд можно рассматривать как границу между программным обеспечением и оборудованием. Классификация микроконтроллеров и микропроцессоры могут быть выполнены на основе архитектуры набора команд RISC и CISC.

Набор инструкций процессора

Набор инструкций определяет функциональность процессора, включая операции, поддерживаемые процессором, механизмы хранения процессора и способ компиляции программ для процессора.

Что такое RISC и CISC?

В RISC и CISC можно расширить следующим образом:

RISC представляет собой компьютер с сокращенным набором команд и

CISC представляет собой компьютер со сложным набором команд.

Архитектура RISC (компьютер с сокращенным набором команд)

Архитектура RISC

В архитектура микроконтроллера который использует небольшой и высоко оптимизированный набор инструкций, называется компьютером с сокращенным набором инструкций или просто RISC. Это также называется архитектурой ЗАГРУЗКИ / СОХРАНЕНИЯ.

В конце 1970-х - начале 1980-х годов проекты RISC в основном разрабатывались в Стэнфорде, Калифорнийском университете в Беркли и IBM. Джон Кок из исследовательской группы IBM разработал RISC, сократив количество инструкций, необходимых для обработки вычислений быстрее, чем CISC. Архитектура RISC быстрее, а микросхемы, необходимые для производства архитектуры RISC, также дешевле по сравнению с архитектурой CISC.

Типичные особенности архитектуры RISC

- Технология конвейерной обработки RISC позволяет одновременно выполнять несколько частей или этапов инструкций, так что каждая инструкция в ЦП оптимизирована. Следовательно, процессоры RISC имеют тактовую частоту на инструкцию одного цикла, и это называется выполнением за один цикл.

- Это оптимизирует использование реестра с большим количеством регистров в RISC и большем количестве взаимодействий в памяти можно предотвратить.

- Простые режимы адресации, даже сложная адресация может быть выполнена с помощью арифметики И / ИЛИ логические операции .

- Он упрощает конструкцию компилятора за счет использования идентичных регистров общего назначения, что позволяет использовать любой регистр в любом контексте.

- Для эффективного использования регистров и оптимизации конвейерной обработки требуется сокращенный набор команд.

- Количество бит, используемых для кода операции, уменьшается.

- Как правило, в RISC 32 или более регистров.

Преимущества архитектуры процессора RISC

- Из-за небольшого набора инструкций RISC компиляторы языков высокого уровня могут создавать более эффективный код.

- RISC позволяет свободно использовать пространство на микропроцессоры из-за своей простоты.

- Вместо использования стека многие процессоры RISC используют регистры для передачи аргументов и хранения локальных переменных.

- Функции RISC используют только несколько параметров, а процессоры RISC не могут использовать инструкции вызова и, следовательно, используют инструкции фиксированной длины, которые легко конвейерно.

- Скорость операции можно максимизировать, а время выполнения - минимизировать.

- Требуется очень меньшее количество форматов инструкций (менее четырех), небольшое количество инструкций (около 150) и несколько режимов адресации (менее четырех).

Недостатки архитектуры процессора RISC

- С увеличением длины инструкций возрастает сложность выполнения RISC-процессорами из-за цикла символов на инструкцию.

- Производительность процессоров RISC зависит в основном от компилятора или программиста, поскольку знание компилятора играет важную роль при преобразовании кода CISC в код RISC, следовательно, качество сгенерированного кода зависит от компилятора.

- При изменении расписания кода CISC на код RISC, называемом расширением кода, размер увеличивается. И качество этого расширения кода снова будет зависеть от компилятора, а также от набора команд машины.

- Кэш первого уровня процессоров RISC также является недостатком RISC, в котором эти процессоры имеют большие кеши памяти на самом кристалле. Для подачи инструкций они требуют очень системы быстрой памяти .

Архитектура CISC (компьютер со сложным набором команд)

Основное предназначение архитектуры процессора CISC - выполнить задачу за счет меньшего количества сборочных линий. С этой целью процессор построен для выполнения ряда операций. Сложная инструкция также называется MULT, которая работает банки памяти компьютера напрямую, не заставляя компилятор выполнять функции сохранения и загрузки.

Архитектура CISC

Особенности архитектуры CISC

- Для упрощения компьютерной архитектуры CISC поддерживает микропрограммирование.

- CISC имеет большее количество предопределенных инструкций, что упрощает разработку и реализацию языков высокого уровня.

- CISC состоит из меньшего количества регистров и большего количества режимов адресации, обычно от 5 до 20.

- Процессору CISC требуется различное время цикла для выполнения инструкций - многочастотные циклы.

- Из-за сложного набора команд CISC техника конвейерной обработки очень сложна.

- CISC состоит из большего количества инструкций, обычно от 100 до 250.

- Особые инструкции используются очень редко.

- Операнды в памяти управляются инструкциями.

Преимущества архитектуры CISC

- Каждая команда машинного языка группируется в команду микрокода и выполняется соответствующим образом, а затем сохраняется во встроенной памяти главного процессора, что называется реализацией микрокода.

- Поскольку память микрокода работает быстрее, чем основная память, набор инструкций микрокода может быть реализован без значительного снижения скорости по сравнению с аппаратной реализацией.

- Со всем новым набором команд можно справиться, изменив дизайн микропрограммы.

- CISC, количество инструкций, необходимых для реализации программы, может быть уменьшено за счет создания богатых наборов инструкций, а также может быть сделано для более эффективного использования медленной основной памяти.

- Благодаря расширенному набору инструкций, который состоит из всех более ранних инструкций, это упрощает микрокодирование.

Недостатки CISC

- Количество часов, затрачиваемое разными инструкциями, будет различным - из-за этого производительность машины замедляется.

- Сложность набора команд и аппаратного обеспечения микросхемы возрастает, поскольку каждая новая версия процессора состоит из подмножества более ранних поколений.

- Только 20% существующих инструкций используются в типичном программном событии, хотя существует множество специализированных инструкций, которые даже не используются часто.

- Условные коды устанавливаются инструкциями CISC как побочный эффект каждой инструкции, для которой требуется время для этой настройки, и, поскольку последующая инструкция изменяет биты кода условия, компилятор должен проверить биты кода условия, прежде чем это произойдет.

RISC Vs. CISC

- Программист может предотвратить ненужные циклы, удалив ненужный код в RISC, но использование кода CISC приводит к потере циклов из-за неэффективности CISC.

- В RISC каждая инструкция предназначена для выполнения небольшой задачи, так что для выполнения сложной задачи несколько небольших инструкций используются вместе, тогда как для выполнения одной и той же задачи с использованием CISC требуется всего несколько инструкций, поскольку она способна выполнять сложную задачу. так как инструкции похожи на высокоязычный код.

- CISC обычно используется для компьютеров, а RISC используется для смартфонов, планшетов и других электронных устройств.

На следующем рисунке показано больше различий между RISC и CISC.

RISC Vs. CISC

Таким образом, в этой статье обсуждаются особенности архитектур RISC и CISC, преимущества и недостатки архитектуры процессоров RISC и CISC, а также различия между архитектурами RISC и CISC с кратким представлением. Для получения дополнительной информации об архитектурах RISC и CISC, отправляйте свои запросы, оставляя комментарии ниже.

Фото:

- Набор инструкций процессора от Arstechnica

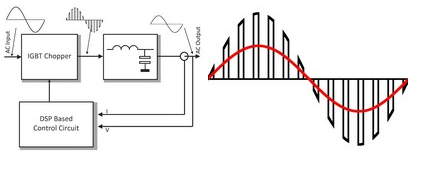

- Архитектура RISC от lsi-contest

- RISC vs. CISC по cs