JTAG (Joint Test Action Group) — это хорошо зарекомендовавший себя стандарт IEEE 1149.1, разработанный в 1980 году для решения производственных проблем, возникающих в электронных платах или устройствах. печатные платы . Эта технология используется для обеспечения достаточного тестового доступа для каждой сложной платы, когда тестовый доступ сокращается. Таким образом, была запущена технология граничного сканирования и стандарт JTAG или Спецификация JTAG Установлено. Сложность электроники растет день ото дня, поэтому спецификация JTAG стала общепринятым форматом тестирования для тестирования сложных и компактных электронных блоков. В этой статье обсуждается обзор JTAG протокол – работа с приложениями.

Что такое JTAG?

Имя, данное стандартному тестовому порту доступа IEEE 1149.1, а также архитектуре граничного сканирования, известно как JTAG (Joint Test Action Group). Эта архитектура граничного сканирования в основном используется в компьютерах. процессоры потому что первый процессор с JTAG выпустила Intel. Этот стандарт IEEE просто определяет, как проверяется схема компьютера, чтобы подтвердить, правильно ли она работает после процедуры производства. На печатных платах проводятся тесты для проверки пайки.

Совместная группа действий по тестированию предоставляет тестерам представление выводов с каждой контактной площадкой ИС, что помогает выявить любые неисправности на печатной плате. Как только этот протокол подключен к чипу, он может подключить зонд к чипу, позволяя разработчику управлять чипом, а также его соединениями с другими чипами. Интерфейс с группой Joint Test Action также может быть использован разработчиками для копирования прошивки в энергонезависимую память электронного устройства.

Конфигурация/вывод

Совместная группа тестовых действий включает 20 контактов, каждый из которых и его функция обсуждаются ниже.

Контакт 1 (VTref): Это контакт целевого опорного напряжения, который используется для подключения к основному источнику питания целевого устройства с напряжением от 1,5 до 5,0 В постоянного тока.

Контакт 2 (Vпитание): Это целевое напряжение питания, которое используется для подключения основного источника напряжения 1,5–5,0 В постоянного тока.

Контакт 3 (nTRST): Это вывод тестового сброса, который используется для сброса конечного автомата TAP-контроллера.

Контакты (4, 6, 8, 10, 12, 14, 16, 18 и 20): Это обычные контакты GND.

Контакт 5 (ТДИ): Это тестовые данные в булавке. Эти данные перемещаются в целевое устройство. Этот штифт должен быть вытащен при определенных условиях на целевой плате.

Pin7 (TMS): Это вывод состояния тестового режима, который извлекается для определения следующего состояния конечного автомата TAP-контроллера.

Контакт 9 (TCK): Это тестовый тактовый вывод, который синхронизирует внутренние операции конечного автомата в TAP-контроллере.

Контакт 11 (RTCK): Это вывод TCK Input Return, который используется в устройствах, поддерживающих адаптивную синхронизацию.

Контакт 13 (TDO): Это контакт вывода тестовых данных, поэтому данные перемещаются из целевого устройства в мухобойку.

Контакт 15 (nSRST): Это контакт сброса целевой системы, который подключен к основному сигналу сброса цели.

Контакты 17 и 19 (НЗ): Это не подключенные контакты.

JTAG работает

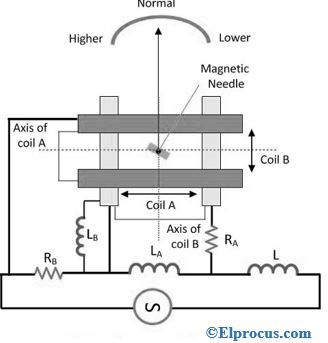

Изначально JTAG использовался для граничного тестирования. Вот простая печатная плата, включающая две микросхемы, такие как ЦП и ПЛИС . Типичная плата может включать множество микросхем. Как правило, ИС включают в себя множество выводов, которые соединены вместе многими соединениями. Здесь, на следующей схеме, показаны только четыре соединения.

Поэтому, если вы проектируете много плат, каждая из которых имеет тысячи соединений. В этом есть несколько плохих досок. Итак, нам нужно проверить, какая плата работает, а какая нет. Для этого была создана Совместная группа тестирования.

Этот протокол может использовать управляющие контакты всех микросхем, но на следующей диаграмме Объединенная группа тестовых действий собирается сделать все выходные контакты ЦП и все входные контакты ПЛИС. После этого, передав некоторое количество данных с выводов ЦП и считывая значения выводов с ПЛИС, JTAG констатирует, что соединения печатной платы в порядке.

На самом деле в группу совместных тестовых действий входят четыре логических сигнала TDI, TDO, TMS и TCK. И эти сигналы должны быть связаны определенным образом. Сначала TMS и TCK подключаются параллельно ко всем микросхемам JTAG.

После этого оба TDI и TDO соединяются для формирования цепочки. Как вы можете заметить, каждая ИС, совместимая с JTAG, включает в себя 4 контакта, которые используются для JTAG, где 3 контакта являются входами, а 4-й контакт является выходом. Пятый контакт, такой как TRST, является необязательным. Обычно выводы JTAG не используются совместно для других целей.

Используя Совместную группу действий по тестированию, все микросхемы используют граничное тестирование, исходная причина которого создана JTAG. В настоящее время использование этого протокола было расширено, чтобы разрешить различные вещи, такие как настройка FPGA, и после этого JTAG используется в ядре FPGA для целей отладки.

JTAG-архитектура

Архитектура JTAG показана ниже. В этой архитектуре все сигналы между основной логикой устройства и контактами прерываются через последовательный путь сканирования, называемый BSR или регистром граничного сканирования. Этот BSR включает в себя различные «ячейки» граничного сканирования. Как правило, эти ячейки граничного сканирования невидимы, но их можно использовать для установки или чтения значений в тестовом режиме с выводов устройства.

Интерфейс JTAG, называемый TAP или Test Access Port, использует различные сигналы для поддержки операции сканирования границ, такие как TCK, TMS, TDI, TDO и TRST.

- Сигнал TCK или Test Clock просто синхронизирует внутренние операции конечного автомата.

- TMS или сигнал выбора тестового режима дискретизируется на нарастающем фронте тестового тактового сигнала для определения следующего состояния.

- Сигнал TDI или Test Data In означает сдвинутые данные в тестовое устройство, в противном случае программируется логика. Как только внутренний конечный автомат находится в правильном состоянии, он выбирается по нарастающему фронту TCK.

- Сигнал TDO или Test Data Out означает сдвинутые данные тестового устройства, иначе программируется логика. Как только внутренний конечный автомат находится в правильном состоянии, он действителен на убывающем фронте TCK.

- TRST или Test Reset — это необязательный контакт, который используется для сброса конечного автомата TAP-контроллера.

TAP-контроллер

Тестовая точка доступа в архитектуре JTAG состоит из TAP-контроллера, регистра команд и регистров тестовых данных. Этот контроллер включает конечный автомат тестирования, который отвечает за считывание сигналов TMS и TCK. Здесь вывод данных i/p просто используется для загрузки данных в граничные ячейки между ядром ИС и физическими выводами, а также для загрузки данных в один из регистров данных или в регистр инструкций. Вывод данных o/p используется для чтения данных либо из регистров, либо из граничных ячеек.

Конечный автомат контроллера TAP управляется TMS и тактируется TCK. Конечный автомат использует два пути для обозначения двух разных режимов, таких как режим инструкций и режим данных.

Регистры

В граничном сканировании доступны два типа регистров. Каждое совместимое устройство включает минимум два или более регистров данных и один регистр инструкций.

Регистр инструкций

Регистр инструкций используется для хранения текущей инструкции. Таким образом, его данные используются TAP-контроллером, чтобы решить, что выполнять с полученными сигналами. Чаще всего данные регистра команд описывают, в какой из регистров данных должны быть переданы сигналы.

Регистры данных

Регистры данных доступны в трех типах: BSR (регистр граничного сканирования), BYPASS и регистр ID CODES. А также могут быть и другие регистры данных, однако они не обязательны как элемент стандарта JTAG.

Регистр граничного сканирования (BSR)

BSR — это основной регистр тестовых данных, который используется для передачи данных от и к контактам ввода-вывода устройства.

БАЙПАС

Bypass — это однобитный регистр, используемый для передачи данных от TDI — TDO. Таким образом, это позволяет тестировать дополнительные устройства в цепи с минимальными затратами.

ИДЕНТИФИКАЦИОННЫЕ КОДЫ

Этот тип регистра данных включает идентификационный код, а также номер версии устройства. Таким образом, эти данные позволяют устройству подключиться к его файлу BSDL (язык описания граничного сканирования). Этот файл содержит сведения о конфигурации сканирования границ для устройства.

Работа JTAG заключается в том, что изначально выбирается режим инструкции, при котором одно из состояний в этом режиме «путь» позволяет оператору синхронизироваться в инструкции по TDI. После этого государственная машина развивается до тех пор, пока не перестроится. Следующим шагом для большинства инструкций является выбор режима данных. Таким образом, в этом режиме данные загружаются через TDI для чтения из TDO. Для TDI и TDO пути данных будут организованы в соответствии с инструкцией, которая была синхронизирована. После завершения операции чтения/записи конечный автомат снова переходит в состояние сброса.

Разница между JTAG и UART

Разница между JTAG и UART заключается в следующем.

| JTAG |

UART |

| Термин «JTAG» расшифровывается как Joint Test Action Group. | Термин ' UART ” означает универсальный асинхронный приемник/передатчик. |

| Это синхронный интерфейс, который использует встроенное оборудование для программирования флэш-памяти. . | UART — это асинхронный интерфейс, в котором используется загрузчик, работающий в памяти. |

| Это набор тестовых портов, которые используются для отладки, но также могут использоваться для программирования прошивки (что обычно и делается).

|

UART — это тип микросхемы, которая управляет обменом данными с устройством, таким как микроконтроллер, ПЗУ, ОЗУ и т. д. В большинстве случаев это последовательное соединение, которое позволяет нам общаться с устройством. |

| Они доступны в четырех типах TDI, TDO, TCK, TMS и TRST. | Они доступны в двух типах UART UART и FIFO UART. |

| Joint Test Action Group — это протокол последовательного программирования или доступа к данным, который используется для взаимодействия микроконтроллеров и связанных с ними устройств. | UART — это один из видов микросхем, в противном случае подкомпонент микроконтроллера, который используется для обеспечения оборудования для генерации асинхронного последовательного потока, такого как RS-232/RS-485. |

| Компонентами JTAG являются процессоры, FPGA, CPLD , так далее. | Компонентами UART являются генератор CLK, регистры сдвига ввода-вывода, буферы передачи или приема, буфер шины системных данных, логика управления чтением или записью и т. д. |

Анализатор протокола JTAG

Анализатор протокола JTAG, такой как PGY-JTAG-EX-PD, является одним из видов анализатора протокола, включающим некоторые функции для захвата и отладки связи между хостом и тестируемым проектом. Этот тип анализатора является ведущим инструментом, который позволяет инженерам-испытателям и проектировщикам тестировать конкретные конструкции JTAG на соответствие их спецификациям путем организации PGY-JTAG-EX-PD, такого как Master или Slave, для генерации JTAG-трафика и декодирования декодированных пакетов Протокол совместной группы действий по тестированию.

Функции

Особенности анализатора протокола JTAG включают следующее.

- Он поддерживает до 25 МГц частот JTAG.

- Он одновременно генерирует JTAG-трафик и декодирует протокол для шины.

- Он имеет мастер-возможности JTAG.

- Переменная скорость передачи данных JTAG и рабочий цикл.

- Пользовательские задержки TDI и TCK.

- Хост-компьютер Интерфейс USB 2.0 или 3.0.

- Анализ ошибок в протоколе декодирования

- Временная диаграмма расшифрованной шины протокола.

- Непрерывная потоковая передача данных протокола на главный компьютер для обеспечения большого буфера.

- Список активности протокола.

- На различных скоростях можно написать сценарий упражнения для объединения нескольких генераций кадров данных.

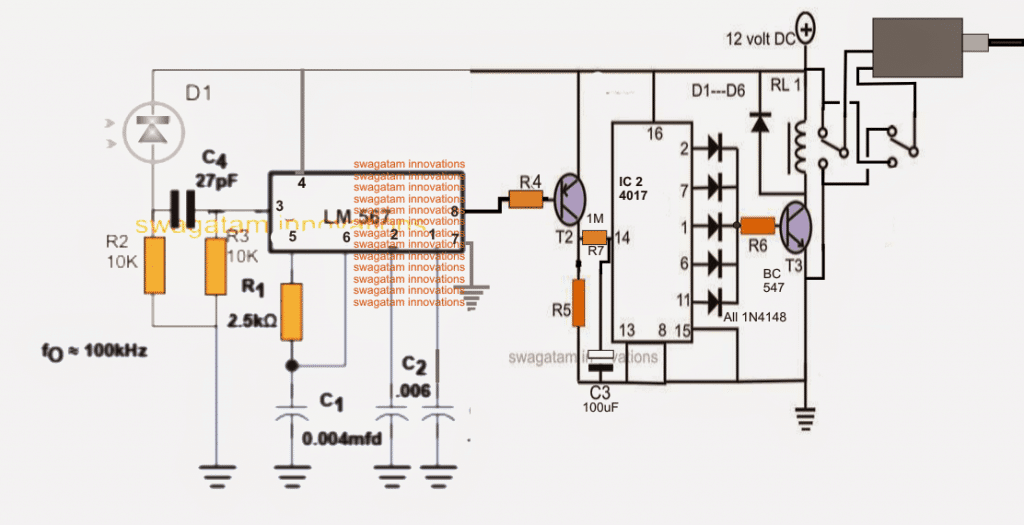

Временная диаграмма

временная диаграмма JTAG протокол показан ниже. На следующей диаграмме вывод TDO остается в состоянии высокого импеданса, за исключением состояний контроллера сдвига-IR/shift-DR.

В условиях контроллера Shift-IR и Shift-DR вывод TDO обновляется по спадающему фронту TCK через Target и замеряется по нарастающему фронту TCK через Host.

Оба вывода TDI и TMS просто опрашиваются по нарастающему фронту TCK через Target. Обновляется по нисходящему фронту, в противном случае TCK через хост.

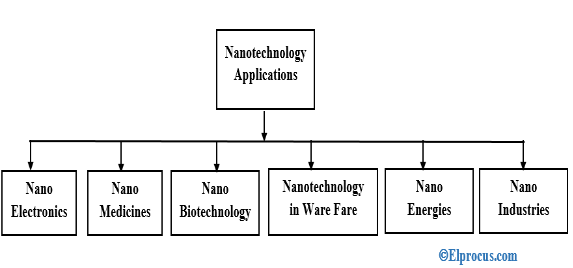

Приложения

JTAG-приложения включая следующее.

- Совместная группа тестовых действий часто используется в процессорах для предоставления права доступа к их функциям эмуляции или отладки.

- Все CPLD и FPGA используют его в качестве интерфейса для предоставления доступа к своим функциям программирования.

- Используется для тестирования печатных плат без физического доступа

- Он используется для производственных испытаний на уровне плат.

Таким образом, это все о обзор JTAG — настройка пинов, работа с приложениями. Промышленный стандарт JTAG используется для проверки конструкции, а также для тестирования печатных плат после изготовления. Вот вопрос к вам, JTAG расшифровывается?